对Stage1页表属性attrindex理解

在看ARM VMSAv8的时候,注意到一个有意思的地方。

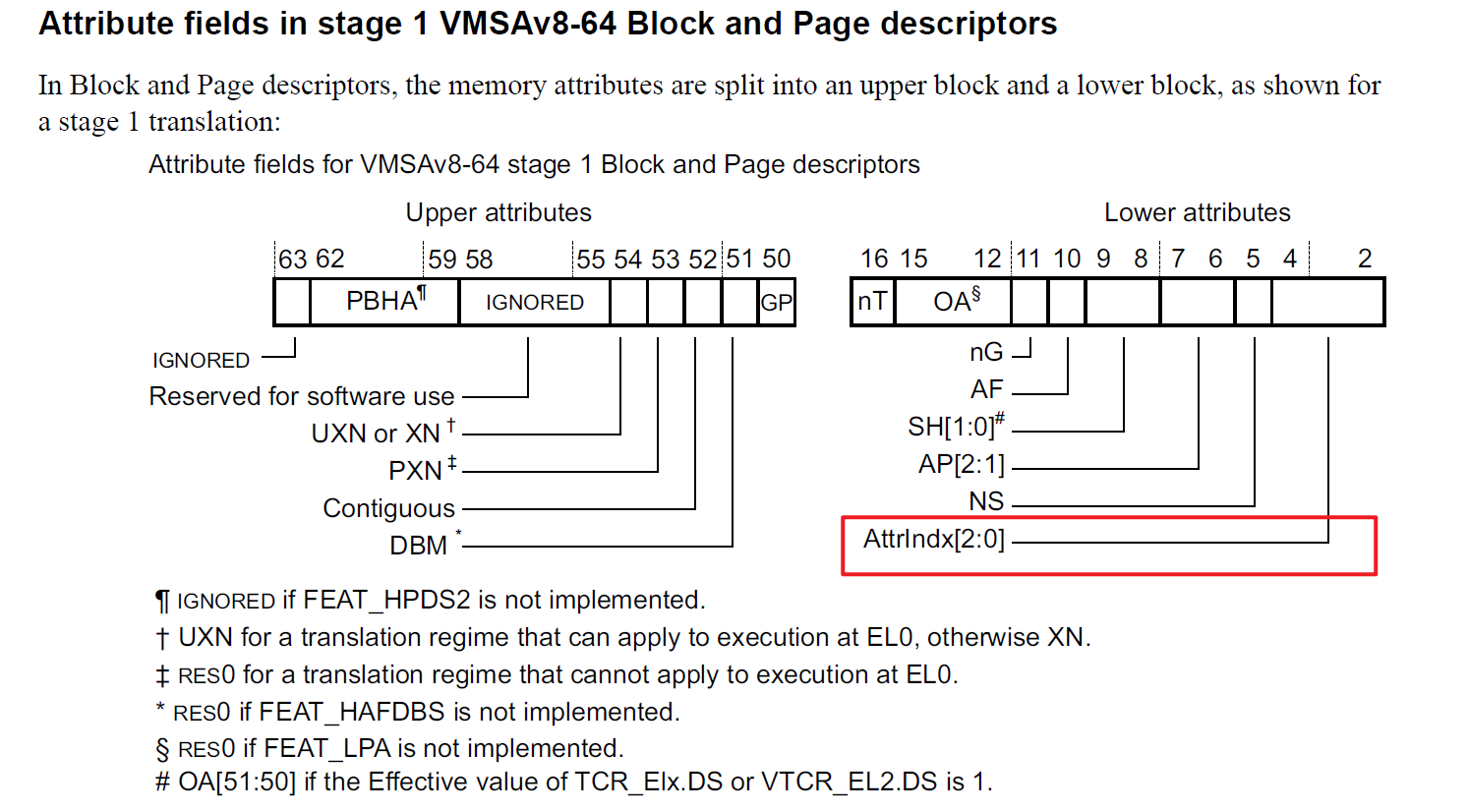

最后获取到page或者block的时候,属性域段中,

stage1的页表最低位属性用的是AttrIndex,

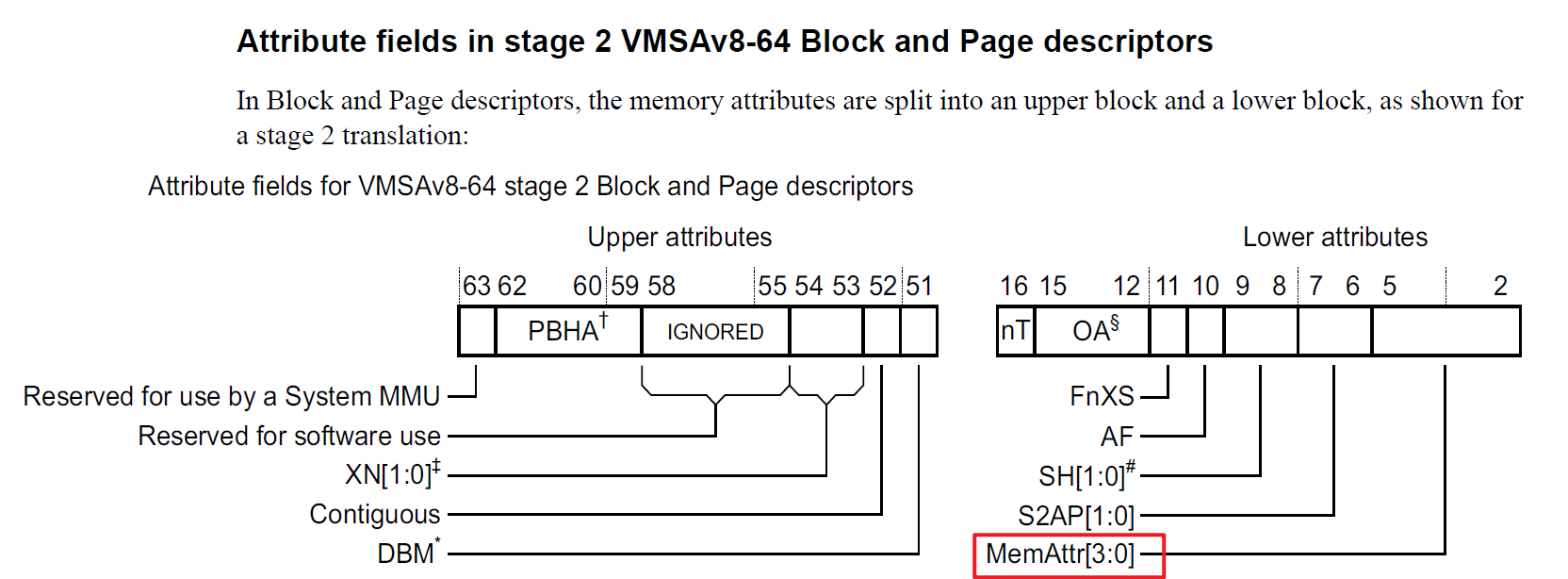

而在stage2的页表属性用的是MemAttr

这两者主要是什么区别呢,也不是很难理解,

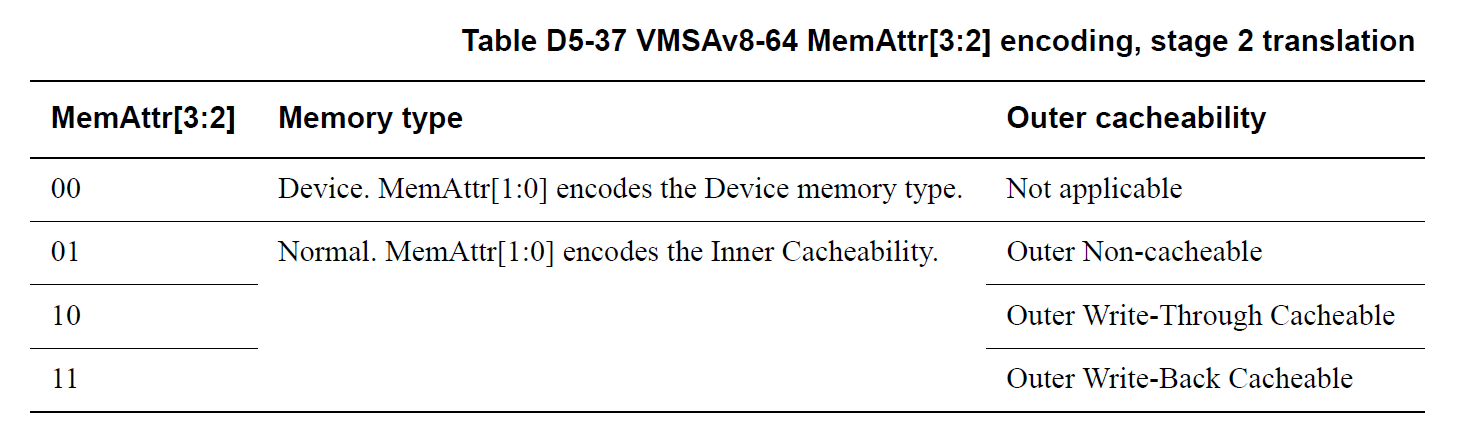

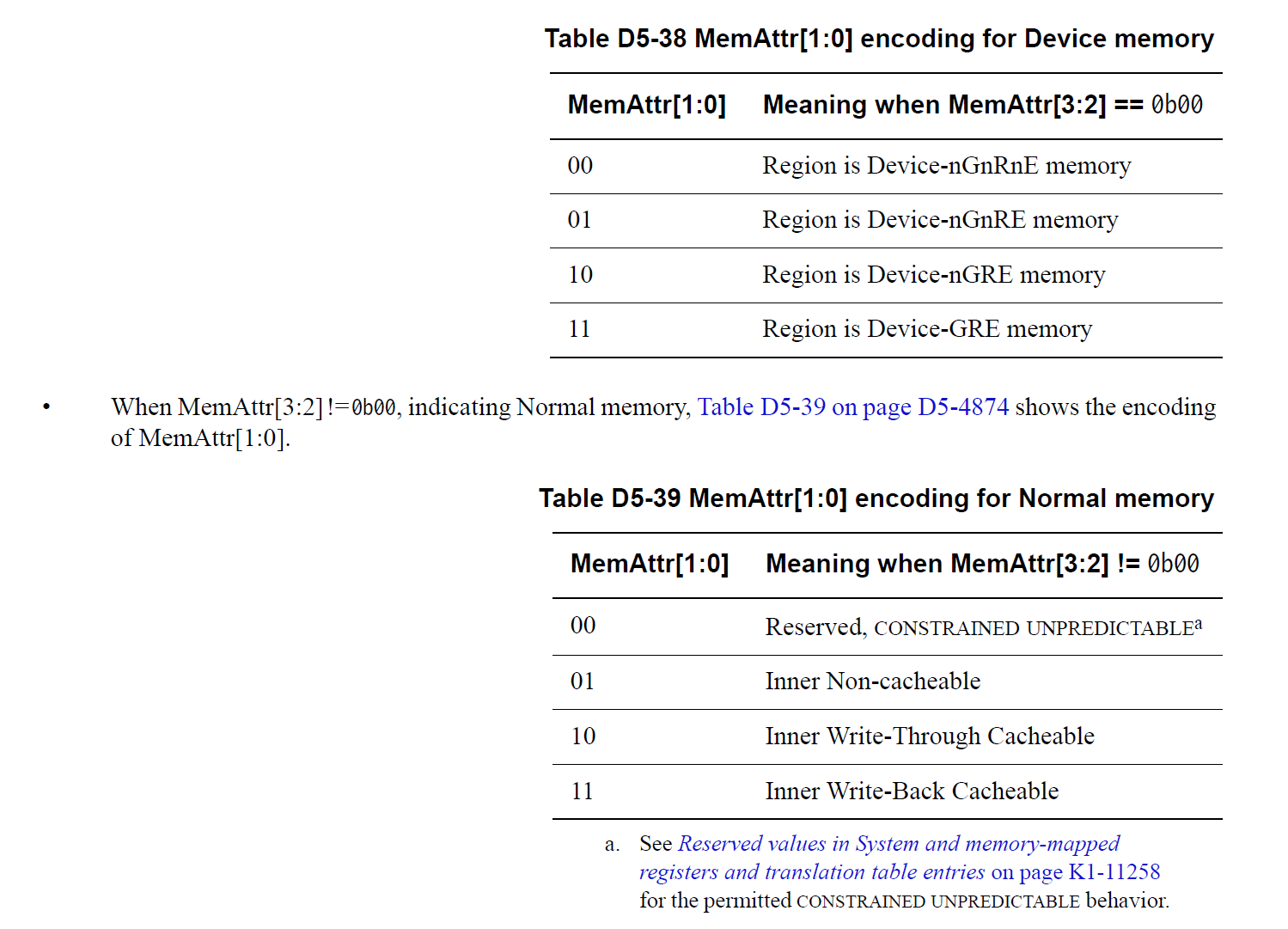

像下面这个,4bit的MenAttr直接就表示memory类型,

高2bit用来区分Device和normal memory的类型。

低2bit用来具体细分是什么device或normal memory类型。

这里就不展开讲了。

重点是上面的stage1 页表,attrindex的使用,它并不是单独就能表示属性的

这个index索引,指的是对MAIR(Memory Attribute Indirection Register)这个寄存器内部进行索引。

MAIR根据不同异常级别有好几个,但其实内部都是一样的,

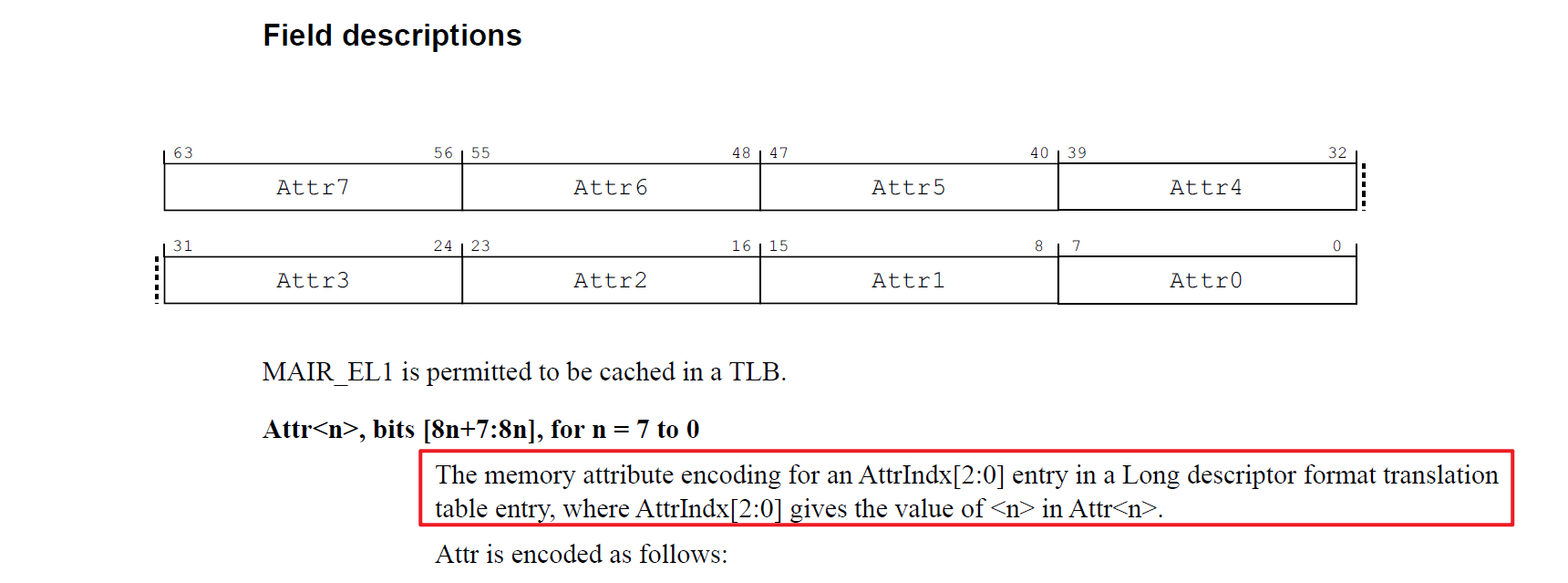

从图上就可以看出,一个64bit的MAIR寄存器中有8个Attr,每8bit为一个Attr。

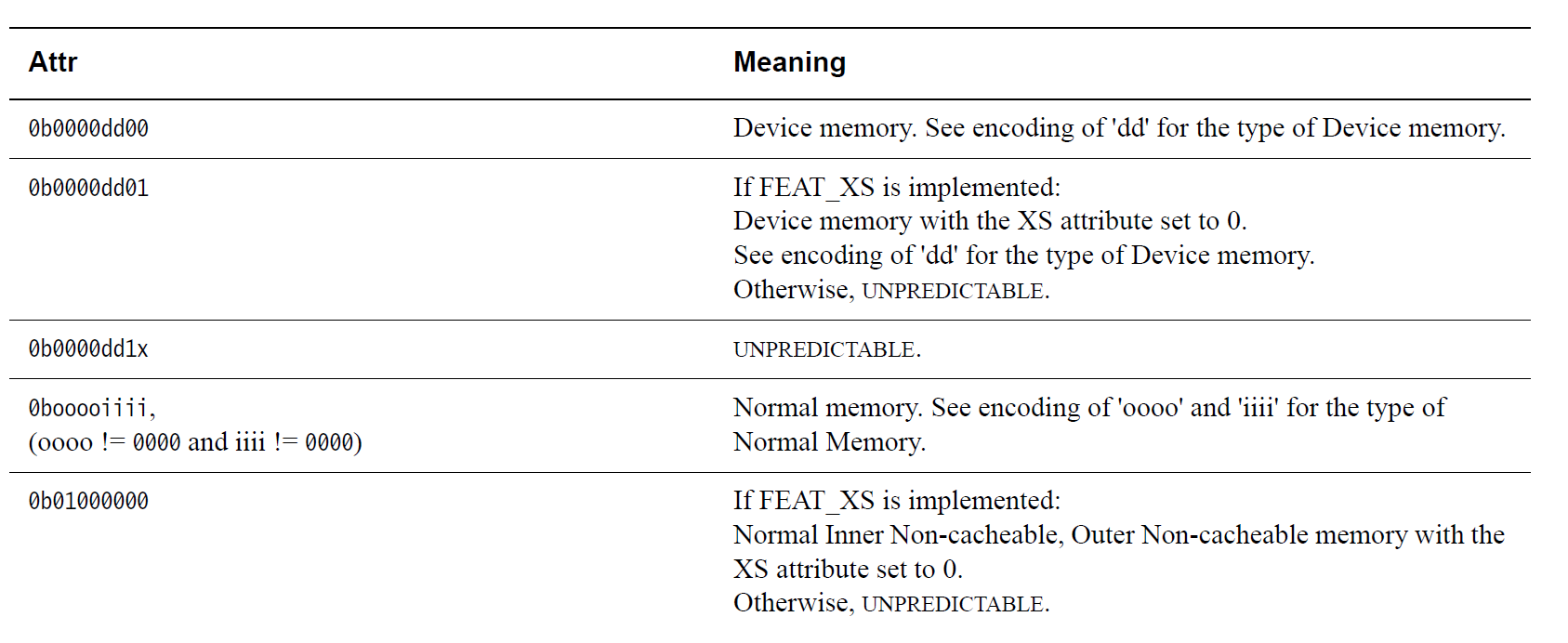

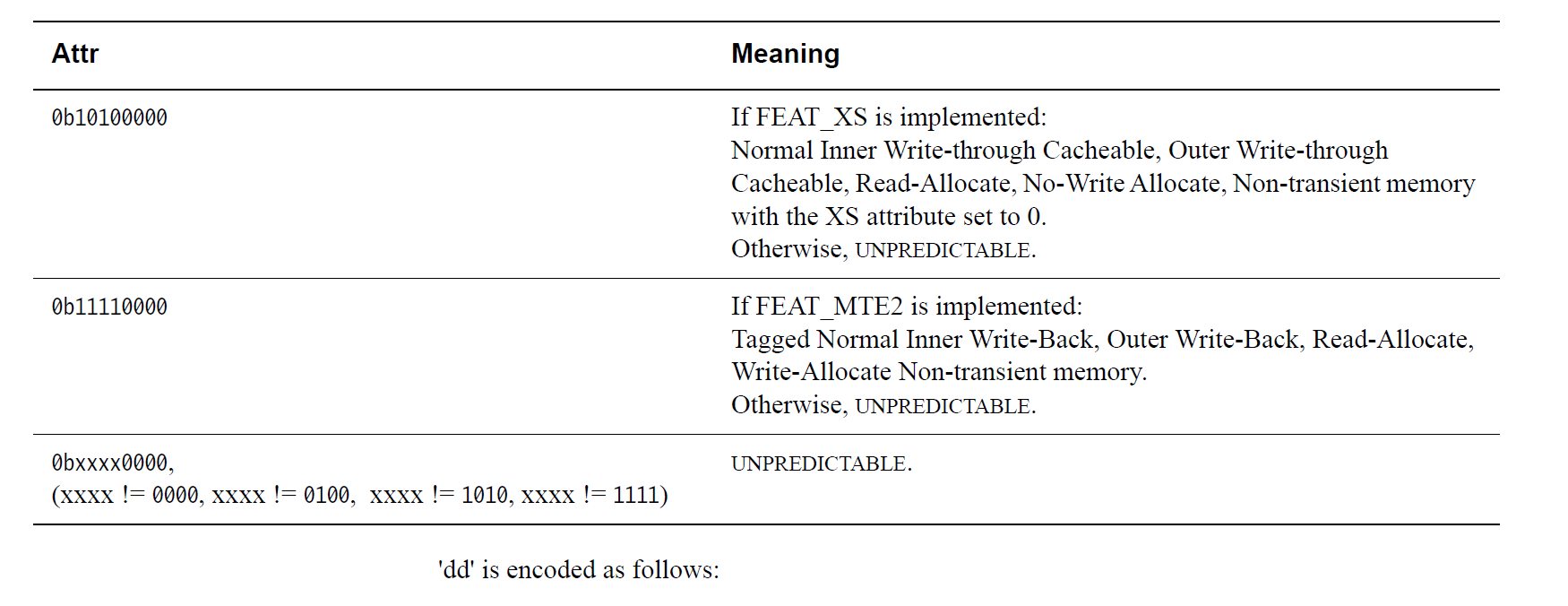

至于这8bit是如何进一步表示属性的,这里也不展开说了,具体可以看架构手册D13.2.97

通过stage1 page中的attrindex属性域段,加上MAIR寄存器中配置的Attr,才能够表示一个地址空间的属性。这样可以理解,但重点在于为什么要这样做。

减少无效化操作,就是这种设计的核心意义。

如果想要改变属性,就需要改页表的话,修改页表后必须发出无效化命令到各个tlb中进行无效化,

而进行无效化的代价其实是很大的。

那为了减少无效化操作,就尽可能不要修改页表,

这里使用attrindex,索引寄存器中配置的属性信息,这意味着如果想要修改属性,仅仅需要修改寄存器值就好了,软件修改寄存器的代价那就比较小了。

至于为什么只有stage1 的页表是这样设计的,还没想太明白。可能终究这样也是需要付出寄存器的代价的,而stage2翻译(虚拟化,IPA->PA)的需求比较小,所以就直接把MemAttr放到页表的属性域段中吧。