从零开始EDA环境搭建

Ubuntu18.04 系统安装

http://mirrors.aliyun.com/ubuntu-releases/18.04/

阿里云镜像下载

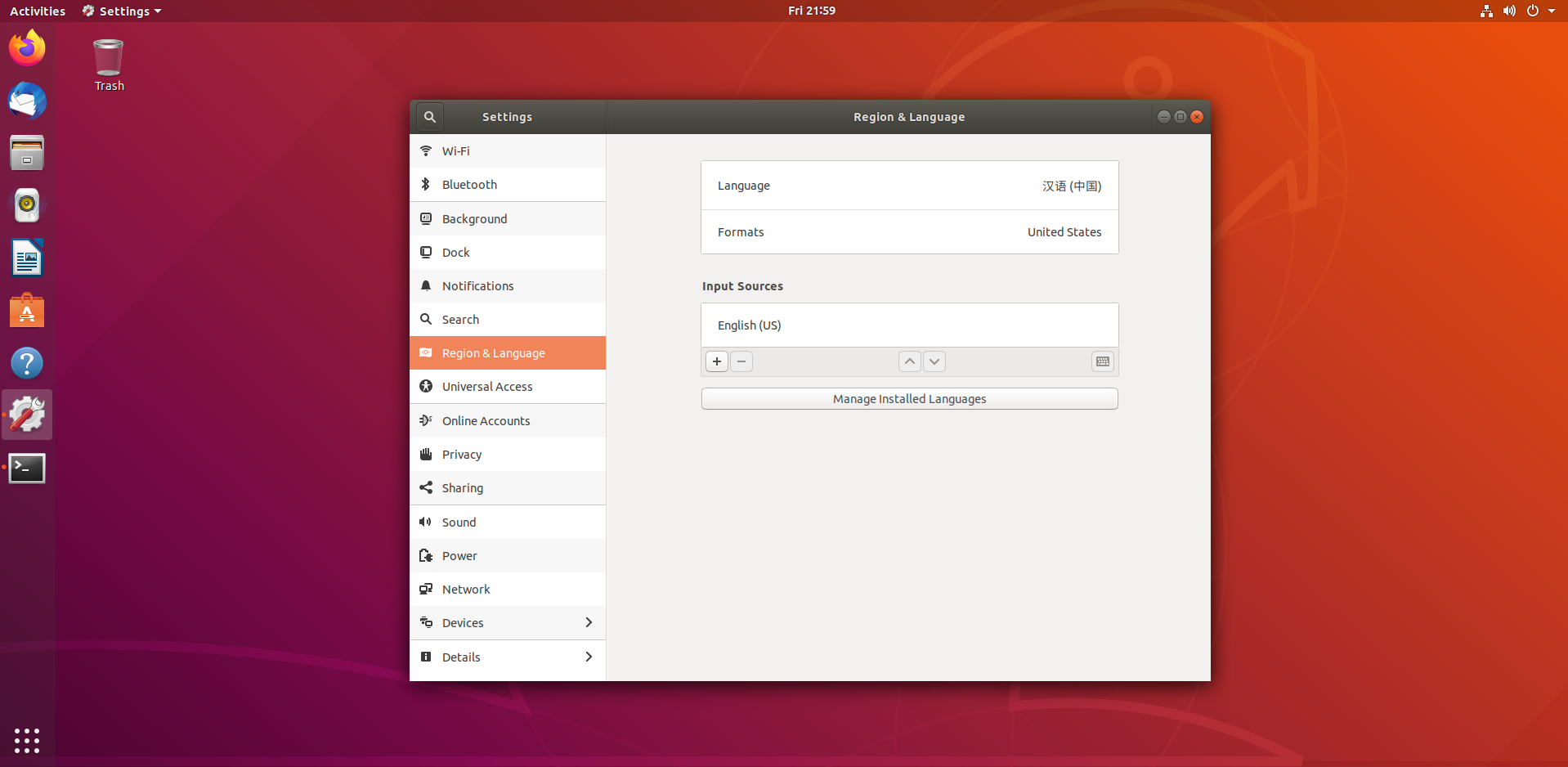

VMware配置安装后,启动后为英文。

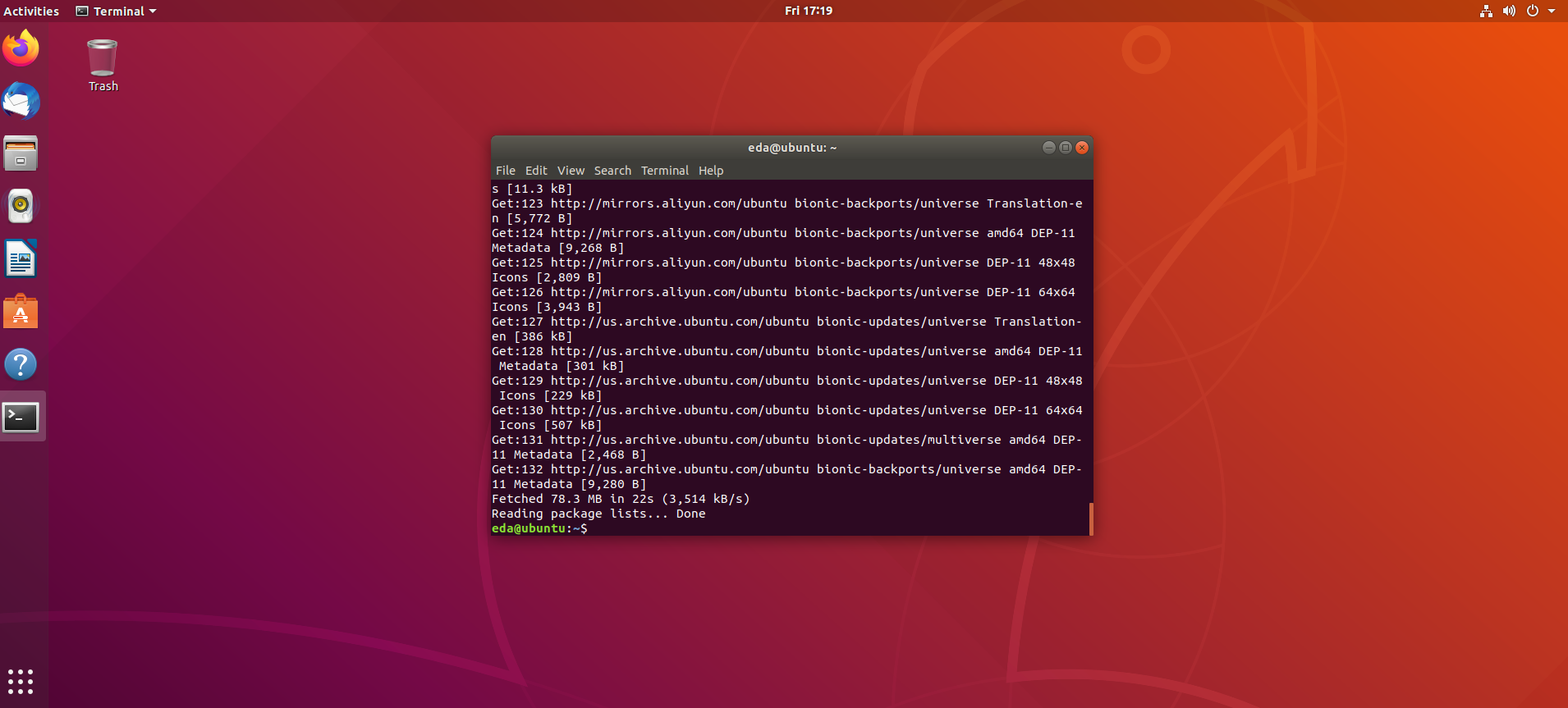

在更改语言前,先换源。

换源

https://zhuanlan.zhihu.com/p/61228593

桌面右键打开terminal

首先备份源列表

sudo cp /etc/apt/sources.list /etc/apt/sources.list_backup

打开sources.list文件

sudo gedit /etc/apt/sources.list

阿里源

deb http://mirrors.aliyun.com/ubuntu/ bionic main restricted universe multiverse

deb http://mirrors.aliyun.com/ubuntu/ bionic-security main restricted universe multiverse

deb http://mirrors.aliyun.com/ubuntu/ bionic-updates main restricted universe multiverse

deb http://mirrors.aliyun.com/ubuntu/ bionic-proposed main restricted universe multiverse

deb http://mirrors.aliyun.com/ubuntu/ bionic-backports main restricted universe multiverse

deb-src http://mirrors.aliyun.com/ubuntu/ bionic main restricted universe multiverse

deb-src http://mirrors.aliyun.com/ubuntu/ bionic-security main restricted universe multiverse

deb-src http://mirrors.aliyun.com/ubuntu/ bionic-updates main restricted universe multiverse

deb-src http://mirrors.aliyun.com/ubuntu/ bionic-proposed main restricted universe multiverse

deb-src http://mirrors.aliyun.com/ubuntu/ bionic-backports main restricted universe multiverse

刷新列表

sudo apt-get update

sudo apt-get upgrade

sudo apt-get install build-essential

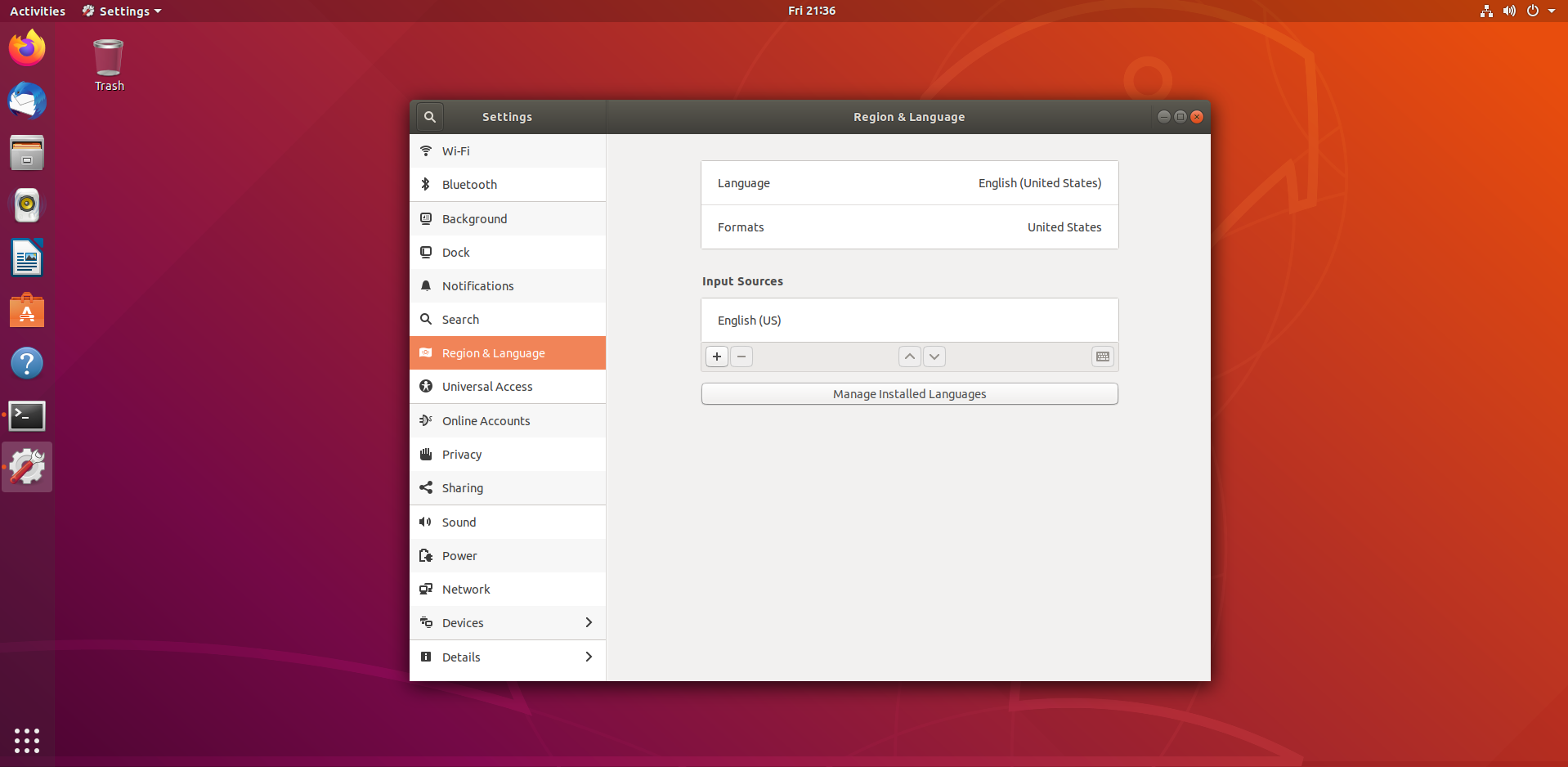

换源以后就可以去下载语言了。

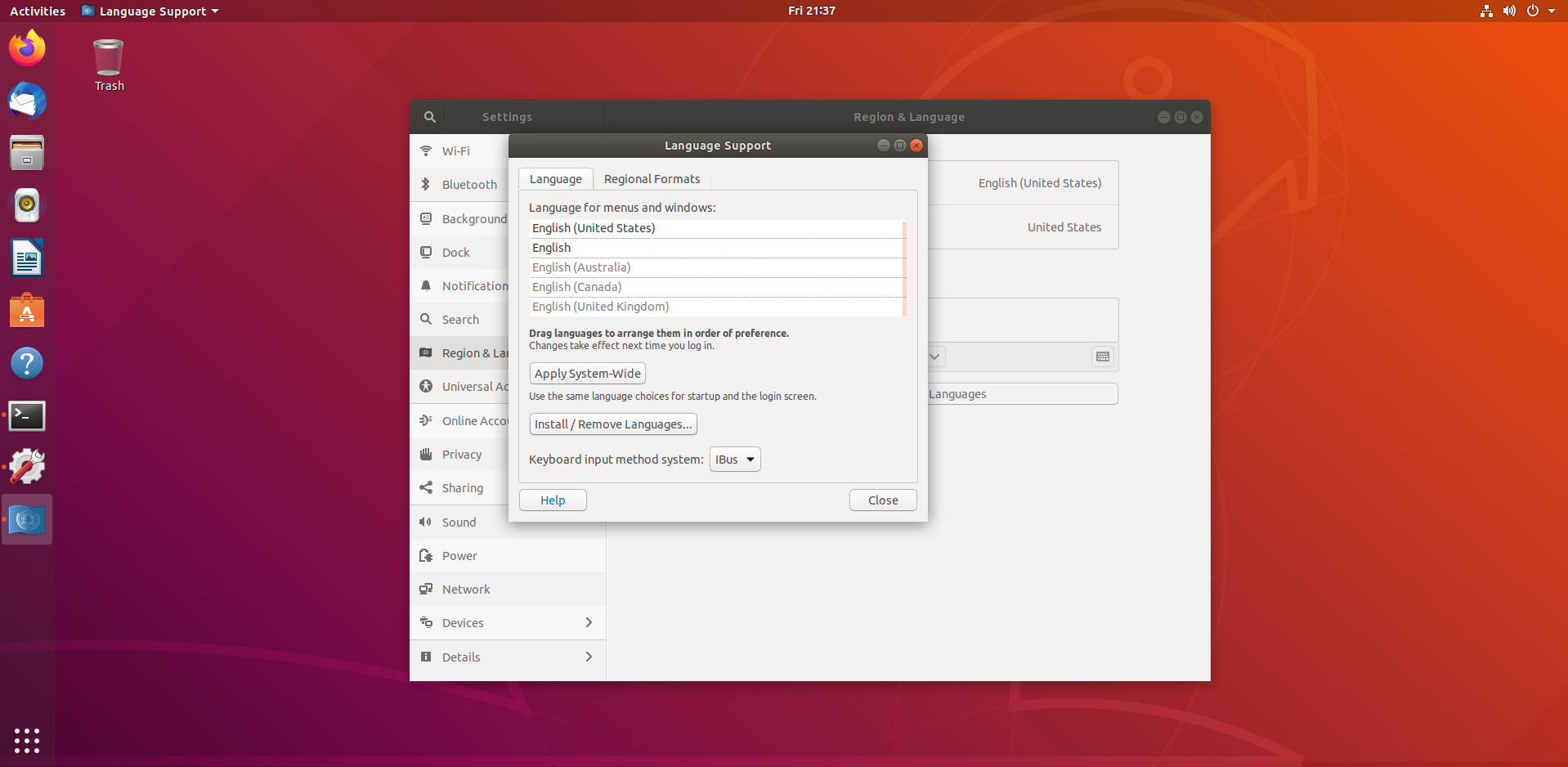

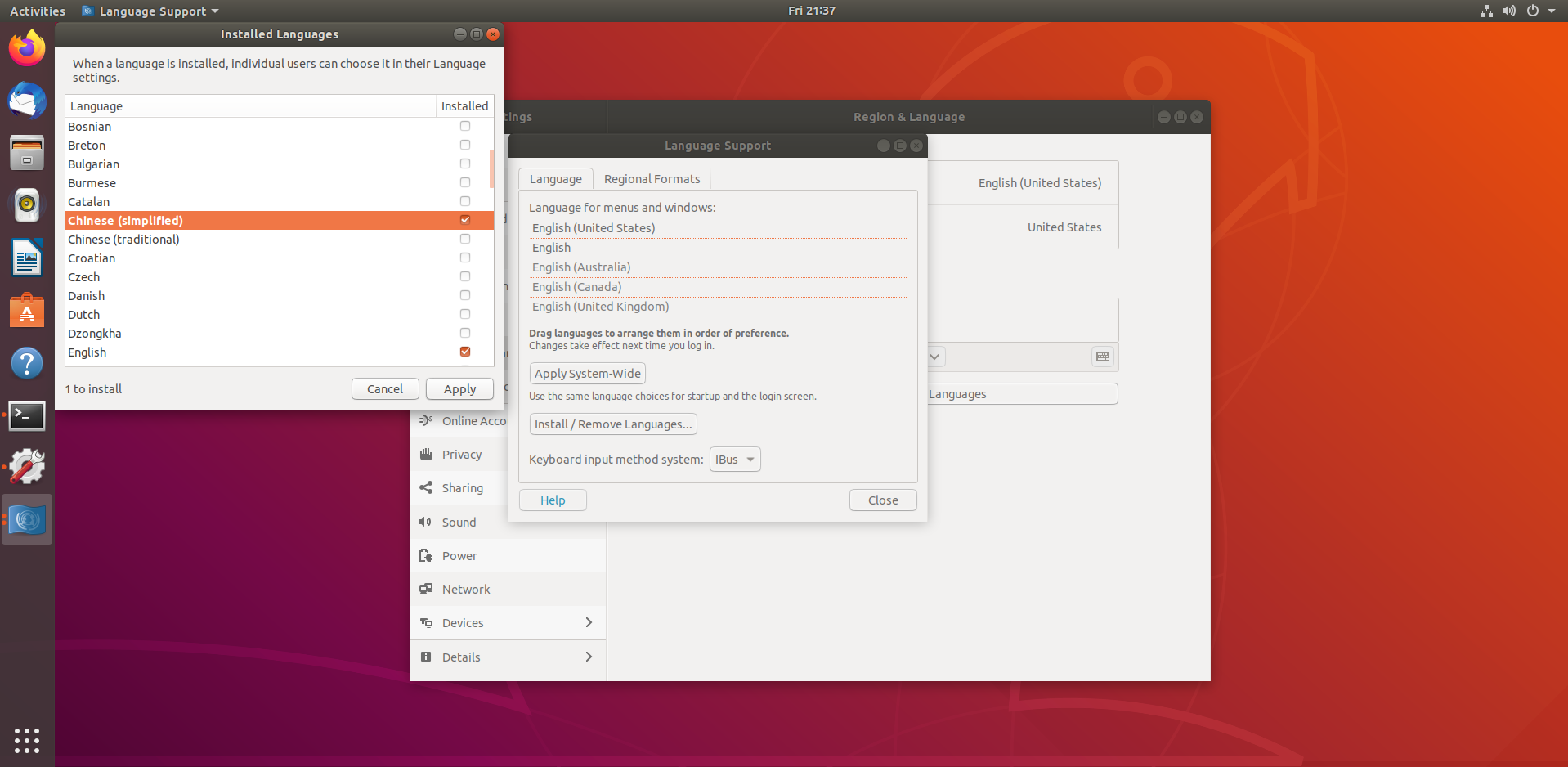

选择下载语言,找到Chinese

更改以后重启。

重启以后提示更改文件夹名称,最好不做修改保持英文。

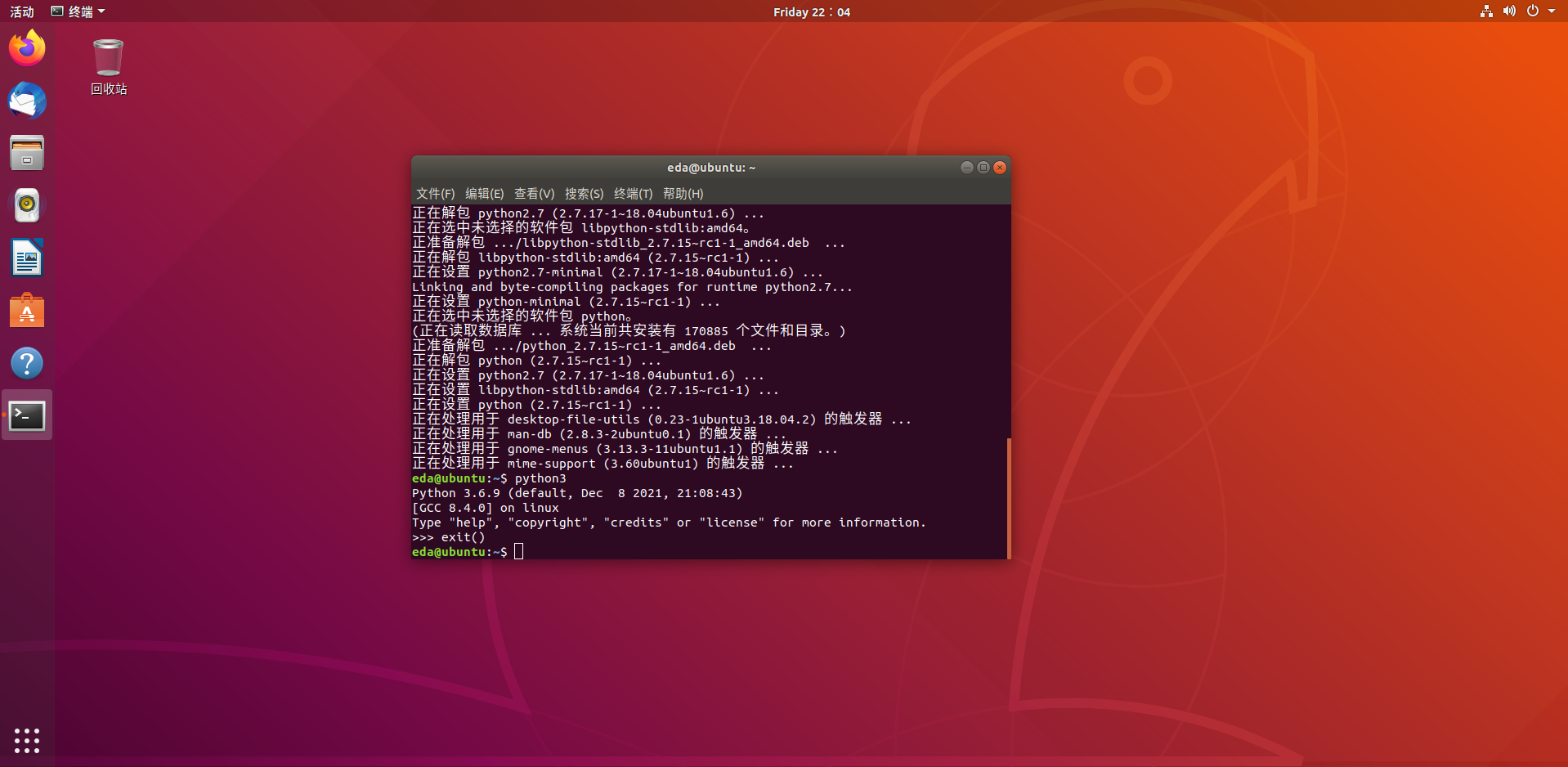

系统不自带python2,补充安装

sudo apt install python

系统自带python3.6.9,应该够用,就不装先了。

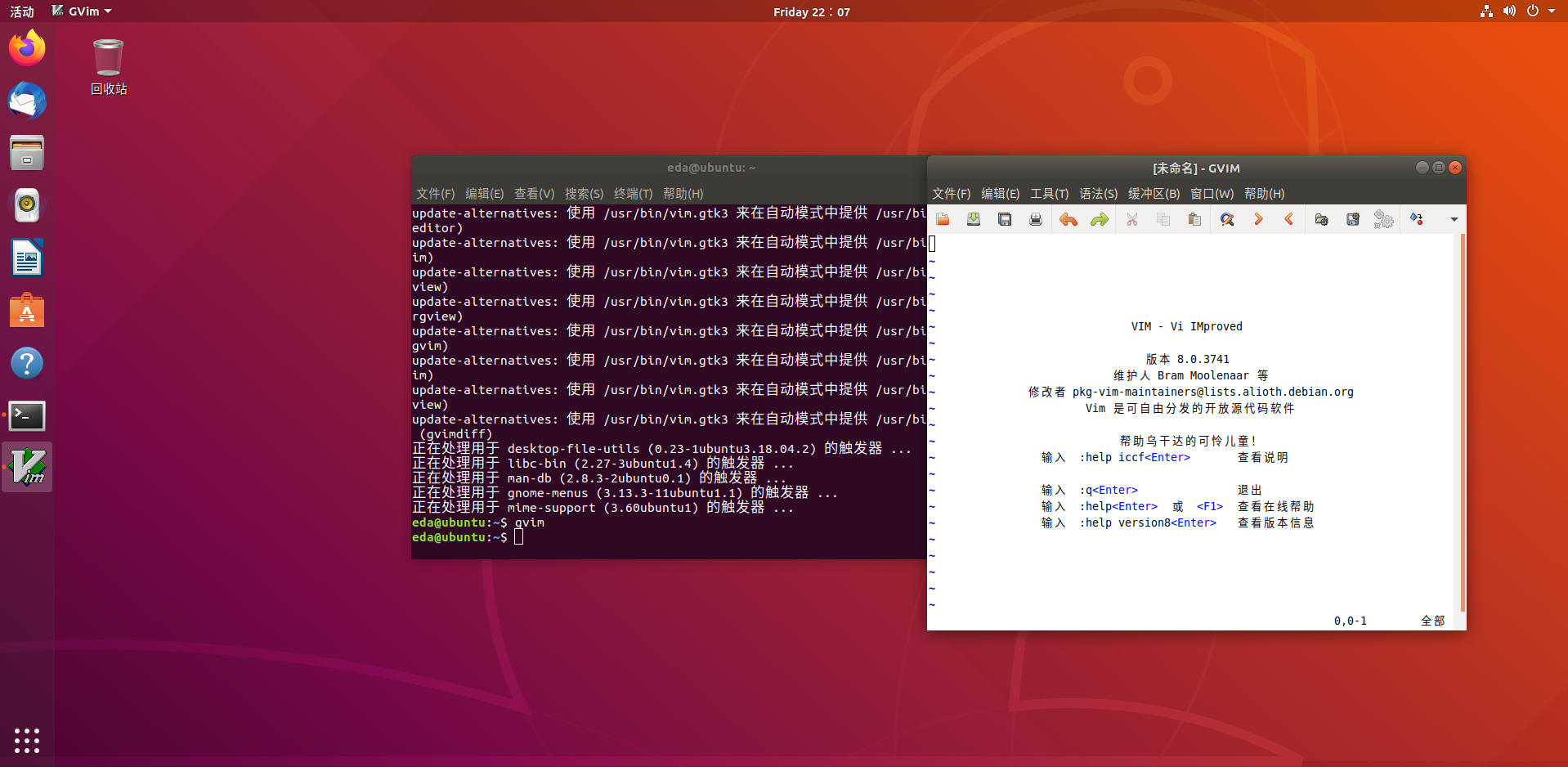

下面开始准备gvim

gvim基本安装

系统自带的vi会出现乱码问题,先卸载

sudo apt-get remove vim-common

重新安装,直接装vim-gtk3

sudo apt install vim-gtk3

基本可以使用了,接下来开始搞插件。

安装git

sudo apt install git

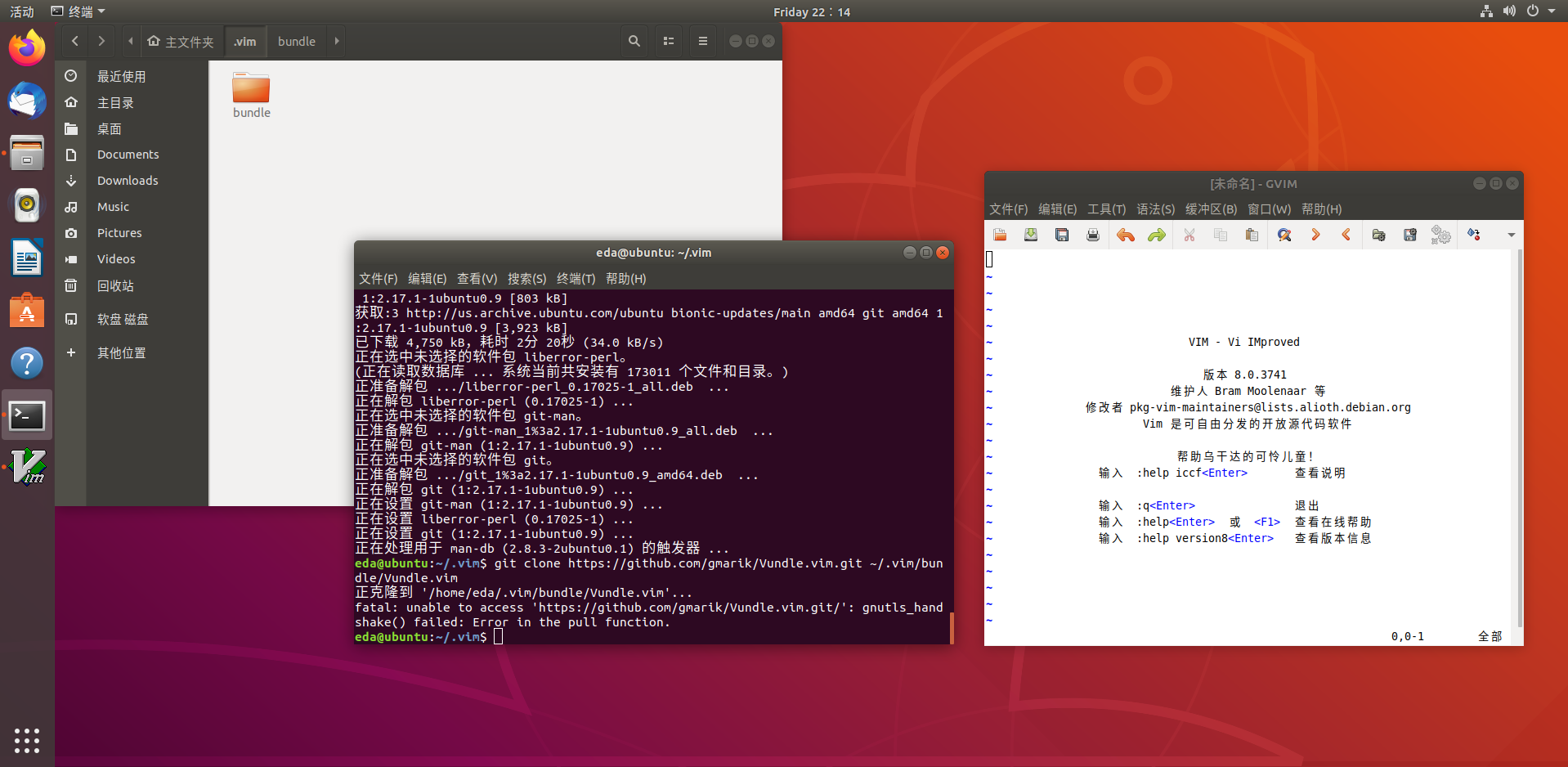

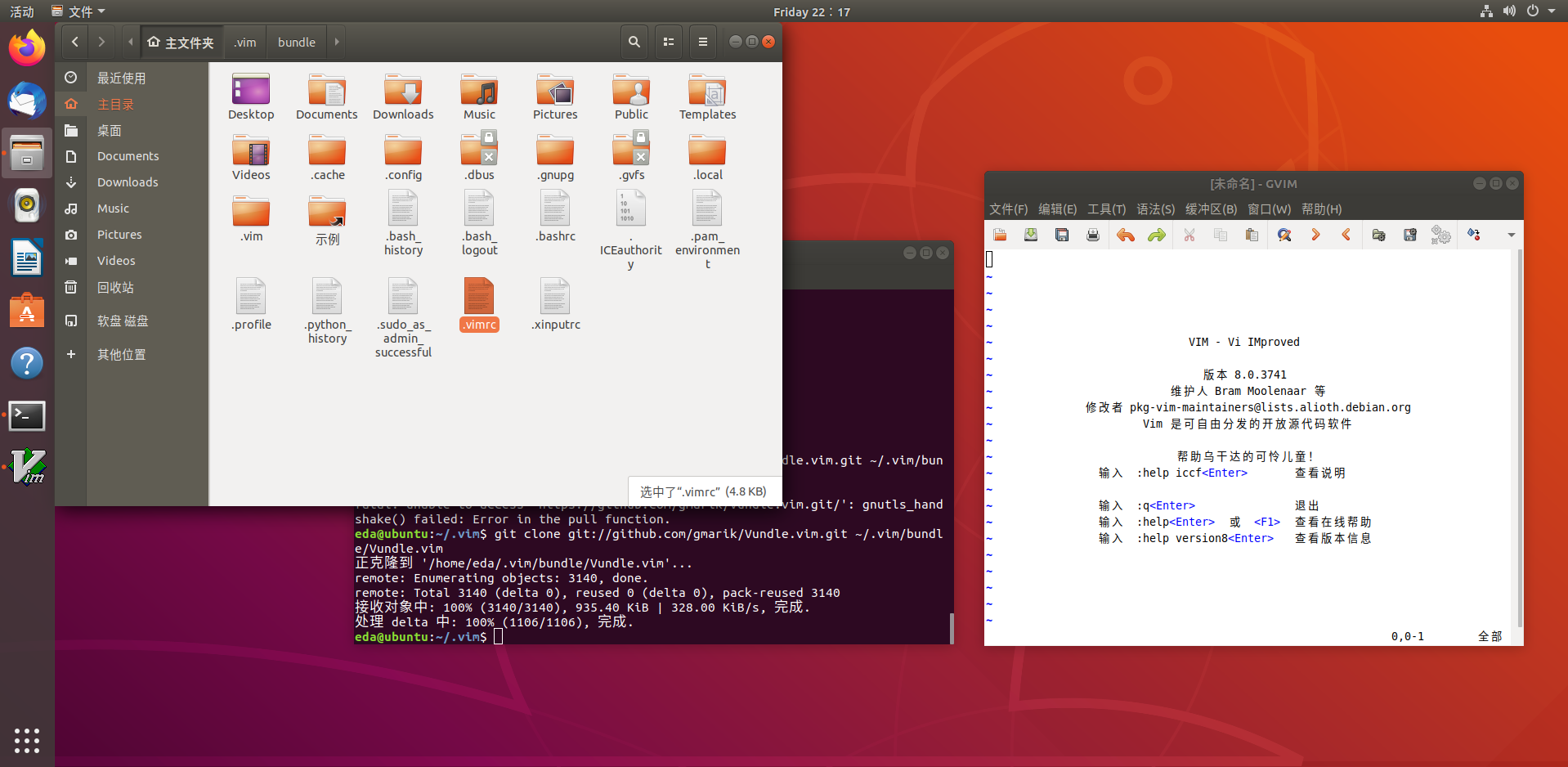

接着首先安装vundle插件管理器

参考https://www.cnblogs.com/feiyuhuo/p/10274236.html

1、先新建目录

mkdir ~/.vim/bundle/Vundle.vim

2、git 克隆 Vundle 工程到本地

git clone https://github.com/gmarik/Vundle.vim.git ~/.vim/bundle/Vundle.vim

出现这个无法访问的提示……

那只能将https修改为git

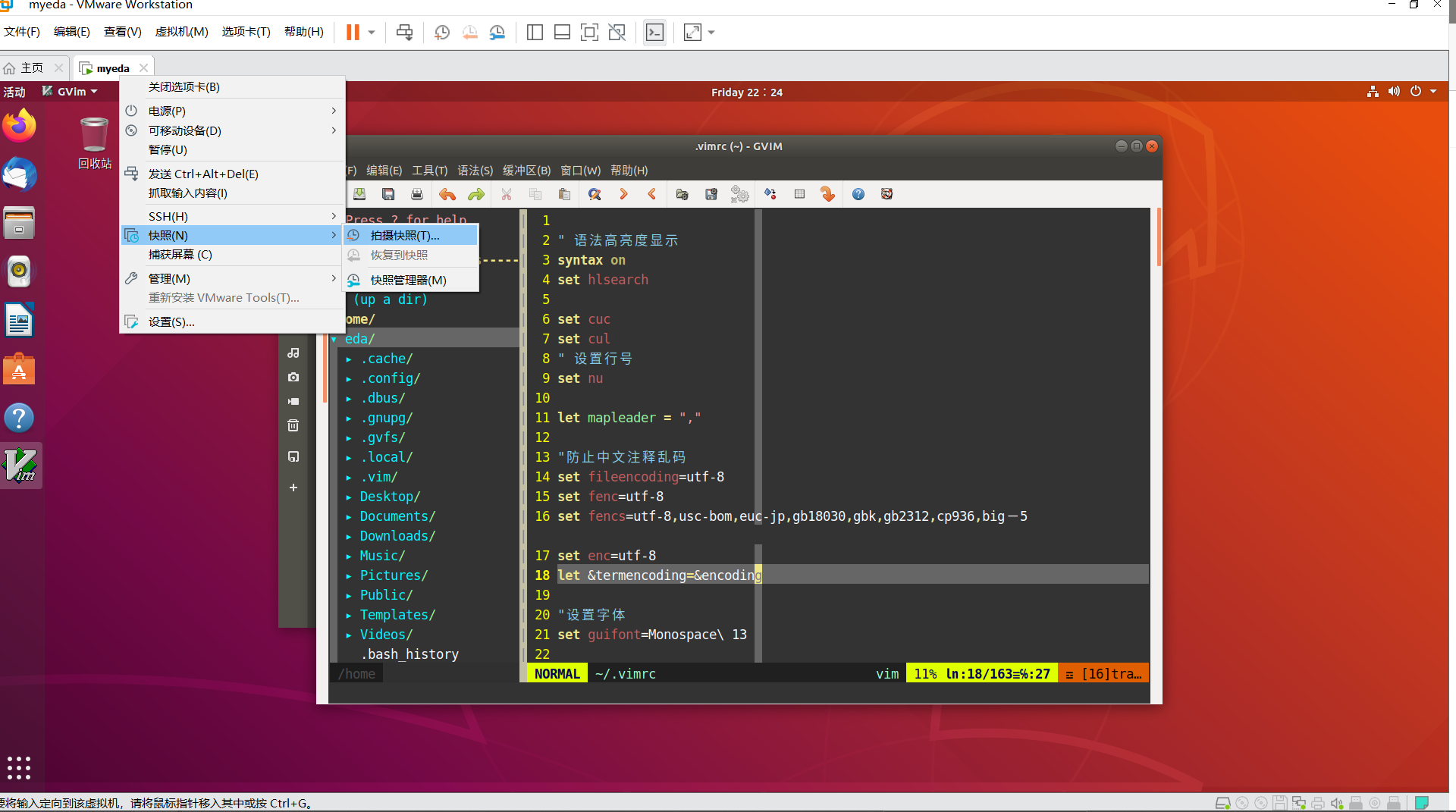

已经准备好的.vimrc文件整个复制进去。【此时目录下应该没有,自己新建一个并命名为.vimrc,然后把下面的内容复制进去即可】

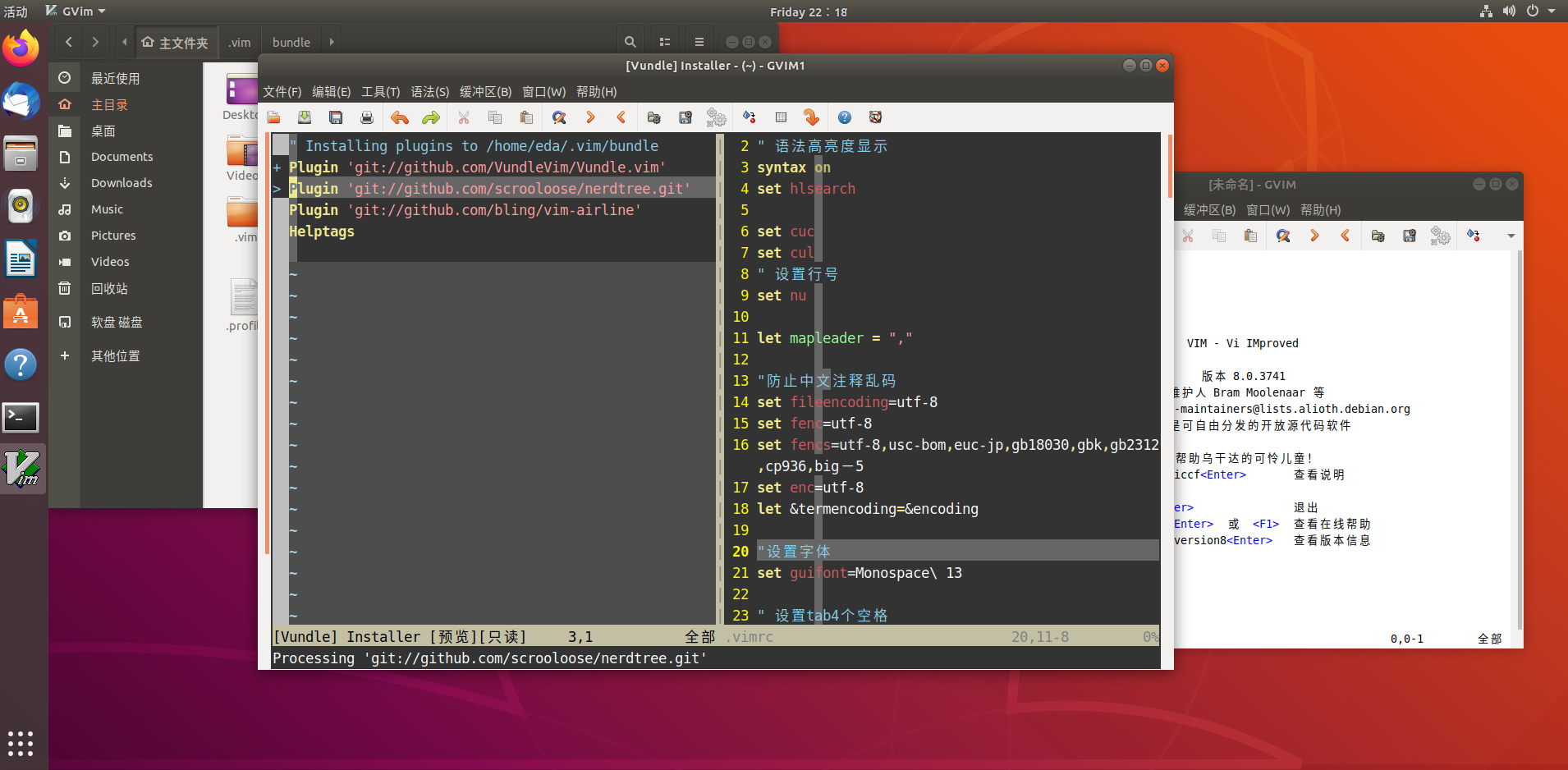

启动gvim,此时会报错无所谓,因为插件还没安装。

回车两下进入正常显示后,输入冒号:PluginInstall安装插件

暂时是只安装三个插件。其他先注释掉了,以后再装。

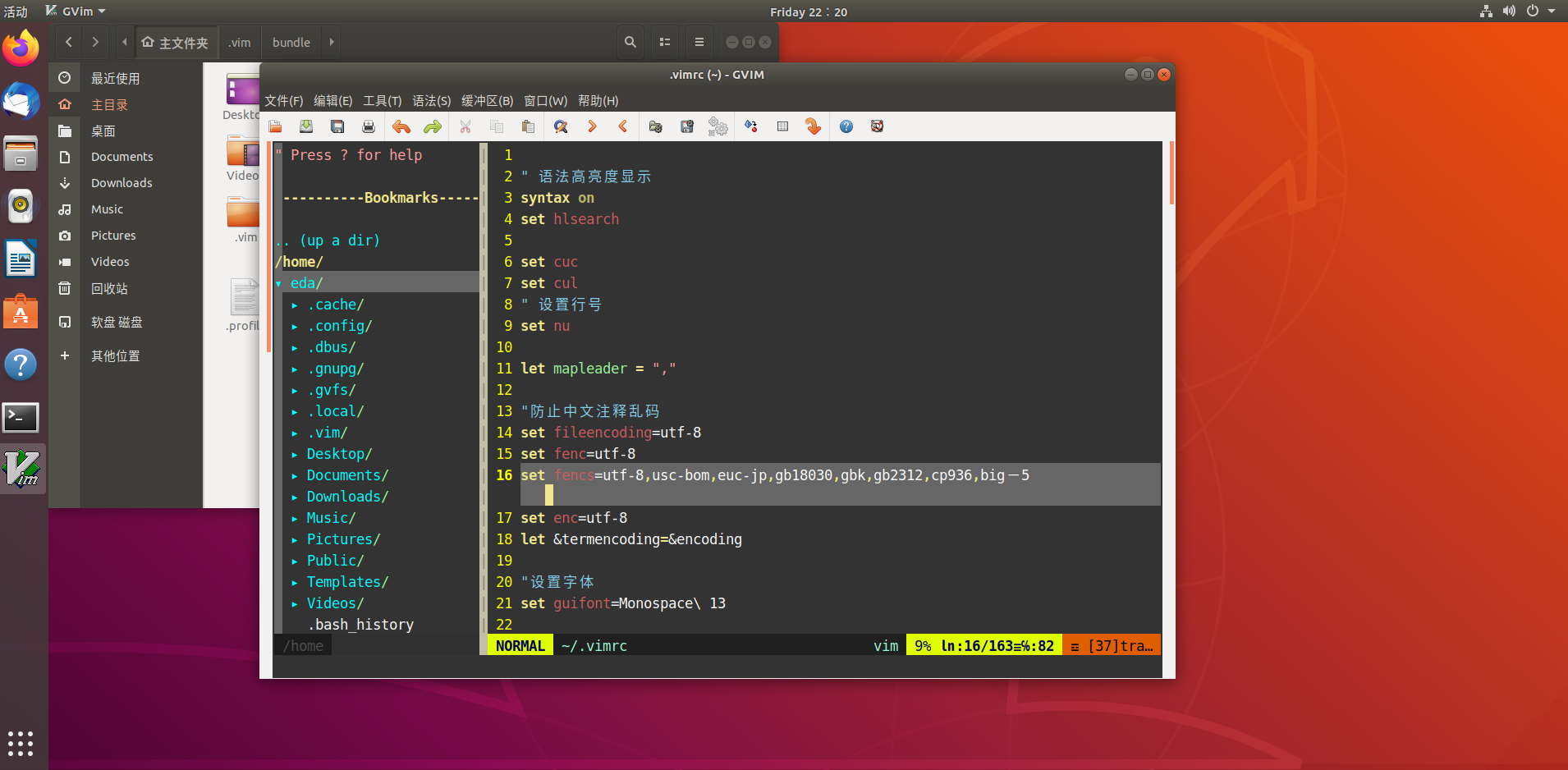

完成以后重启gvim现在已经是比较好看的了。

在~/.vim目录内,新建colors和syntax文件夹

在~/.vim目录内,新建colors和syntax文件夹

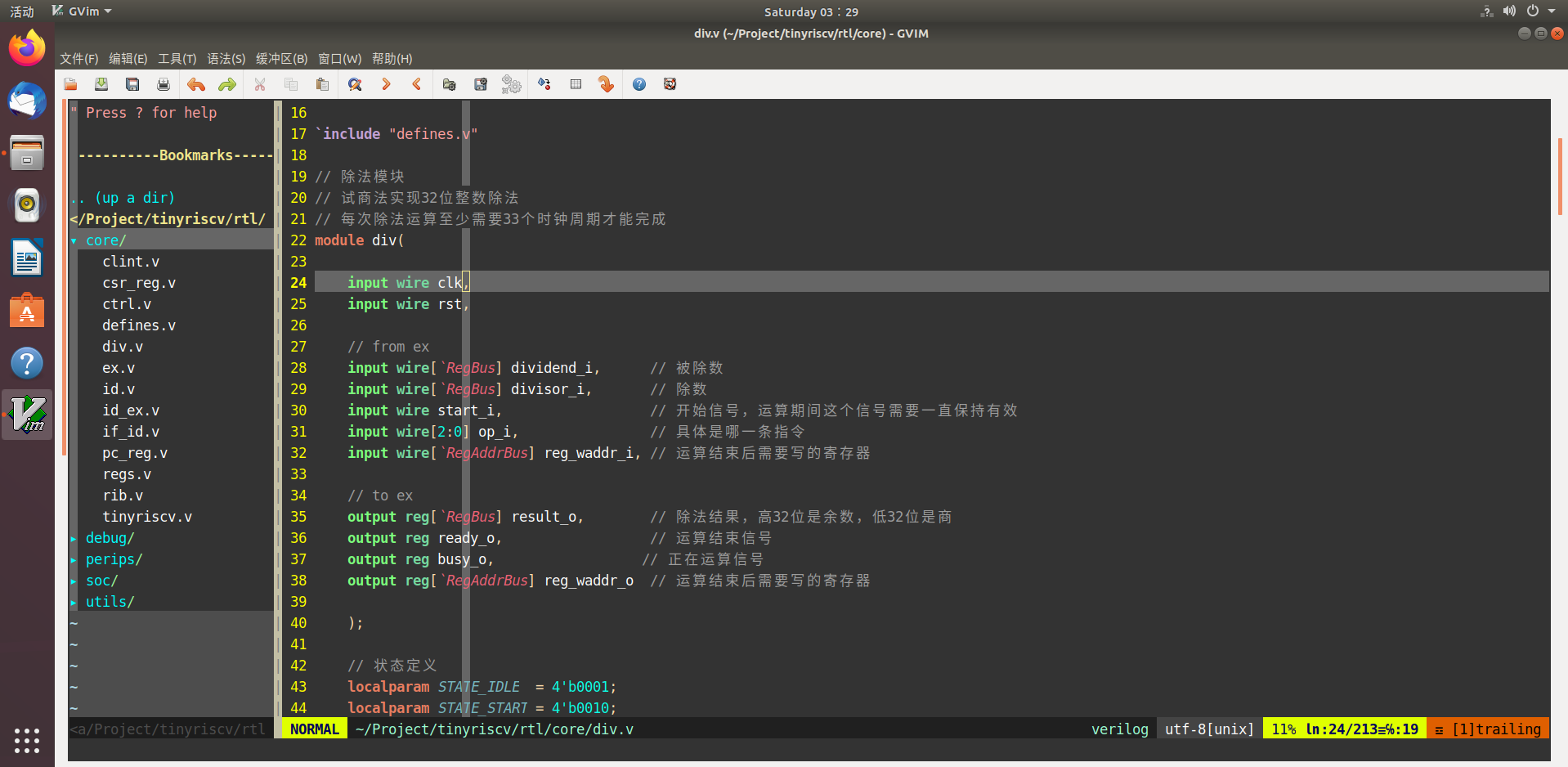

语法文件和色彩方案搭配效果如下

看verilog代码才会有效果。

那么至此最基本的准备就完成了。

先拍摄一个快照保存一下

tinyriscv环境搭建

那么目前是没有多余配置的,

接下来先把tinyriscv的环境准备好。

作者的gitee库

https://gitee.com/liangkangnan/tinyriscv/

在Downloads文件夹下下载iverilog

git clone https://github.com/steveicarus/iverilog.git

cd iverilog

切换到v11分支(必须用V11或以上的版本)

git checkout v11-branch

安装依赖

sudo apt-get install autoconf gperf flex bison build-essential

编译、安装iverilog和vvp

sh autoconf.sh

./configure

sudo make&make install

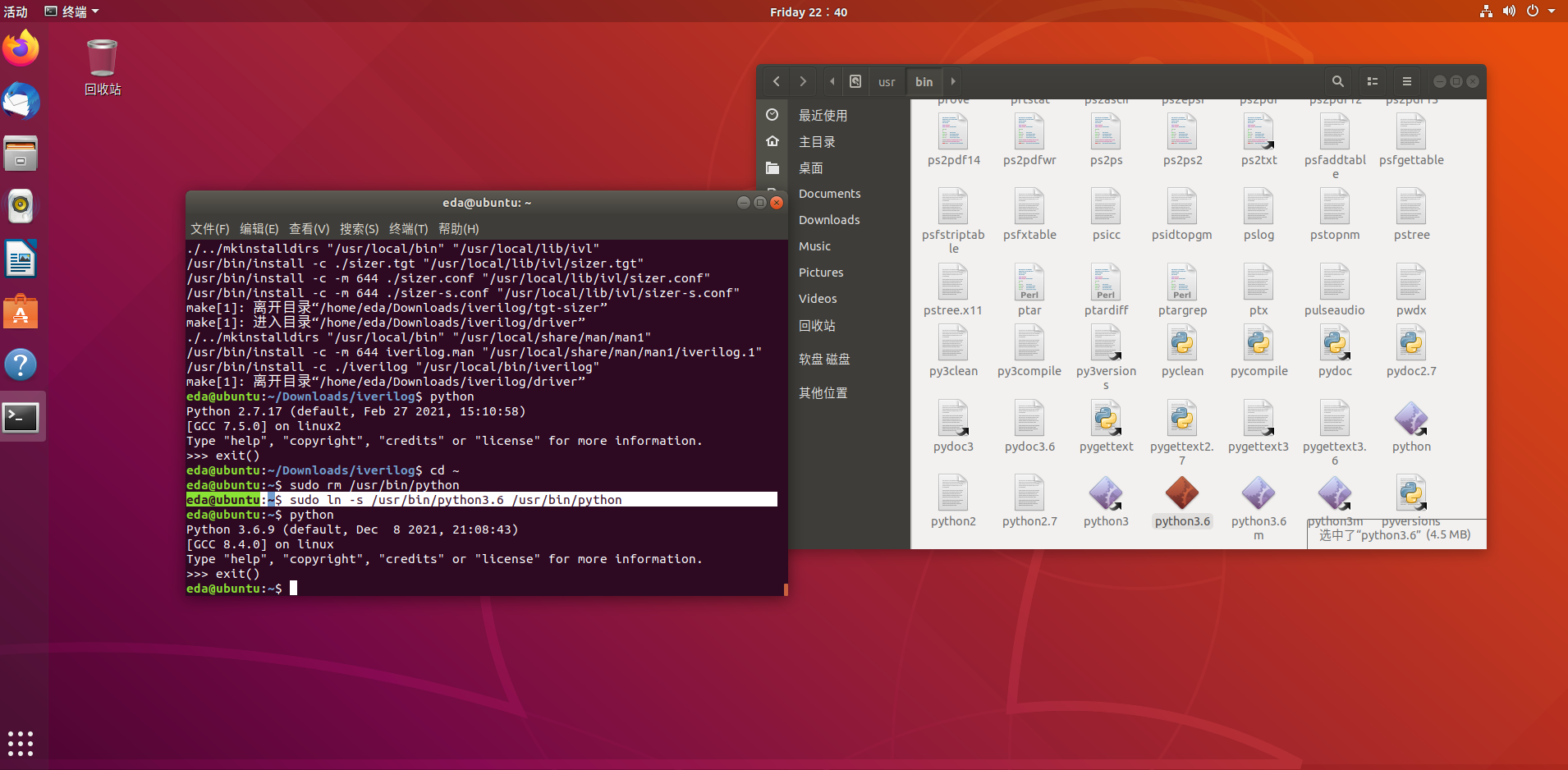

然后准备python3软链接

先删除原来的软链接,这个是连到python2的

sudo rm /usr/bin/python

然后建立新的软链接

sudo ln -s /usr/bin/python3.6 /usr/bin/python

那么现在直接如数python会看到打开的是3.6.9了。exit()退出,接着搞别的。

安装gtkwave

sudo apt-get install gtkwave

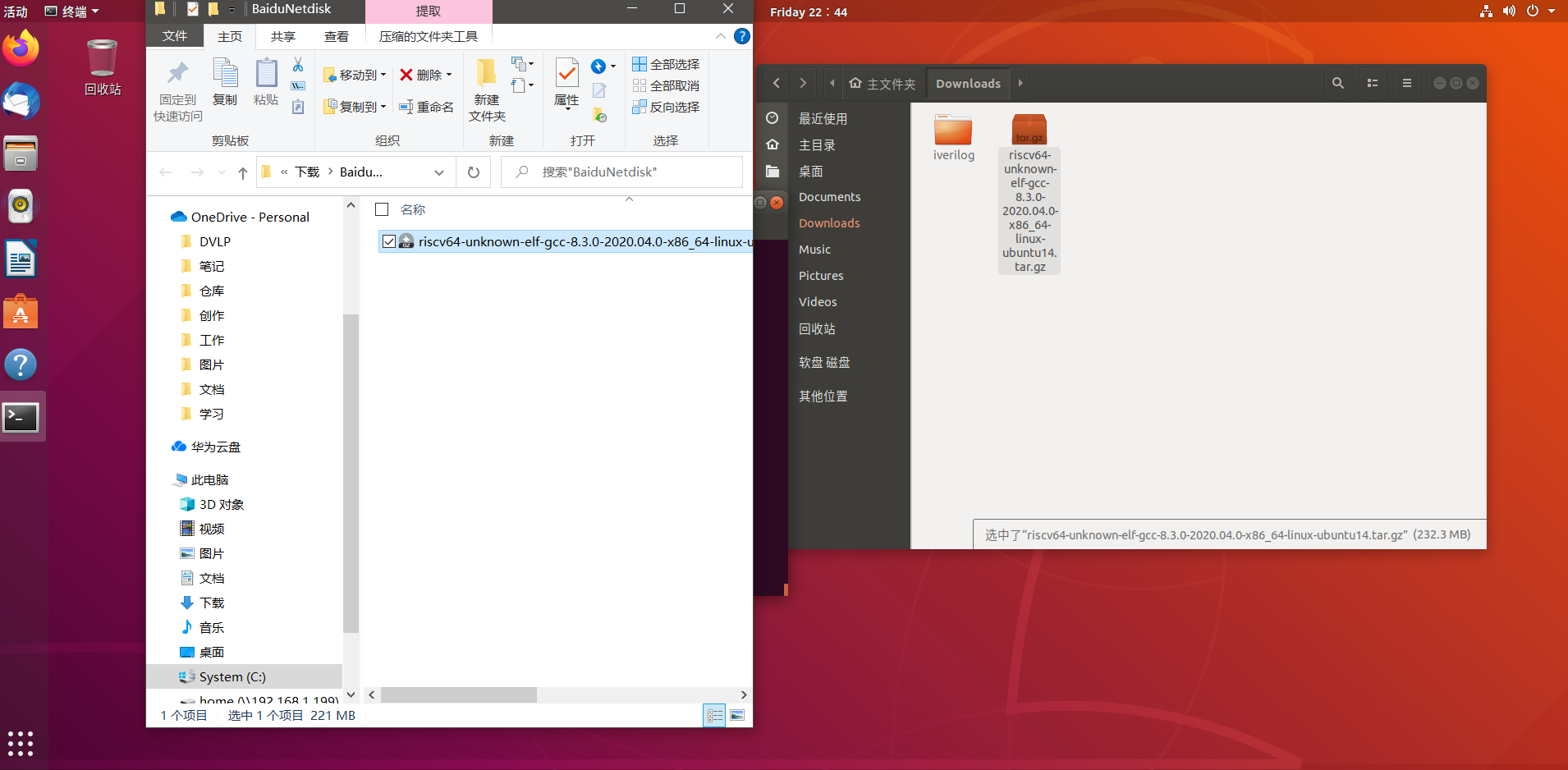

下载gun工具链,百度网盘下载(链接:https://pan.baidu.com/s/10uLZYf_cgtH94kZI_N6JhQ 提取码:uk0w)

然后直接拖拽进去。

右键可以直接解压

接着克隆tinyriscv项目工程

在Downloads目录下克隆

git clone https://gitee.com/liangkangnan/tinyriscv.git

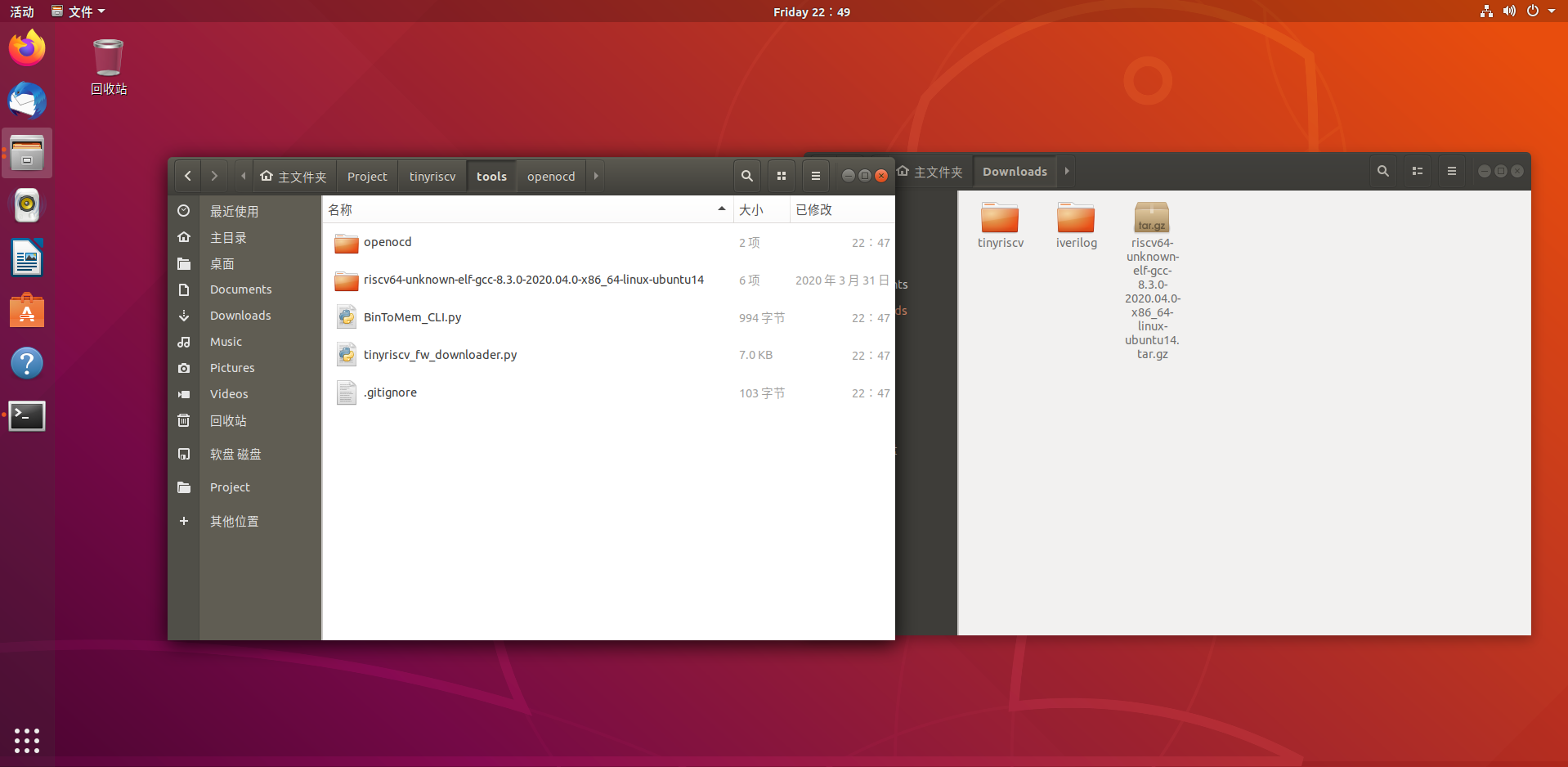

主目录下新建个Project文件夹,将刚克隆的复制过来,之前的作为原始备份。

之前下载的工具链复制到tinyriscv工程下的tools目录中

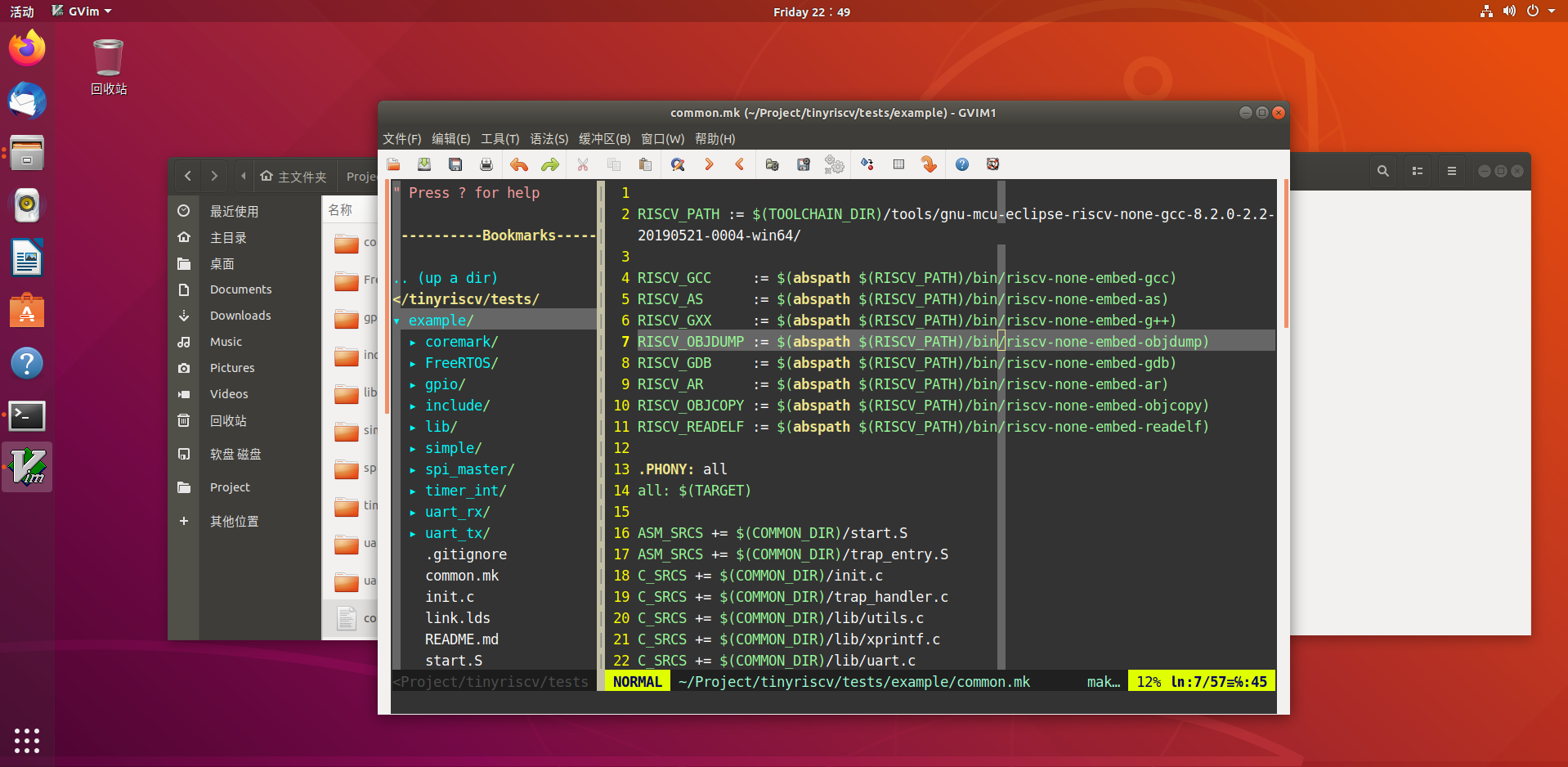

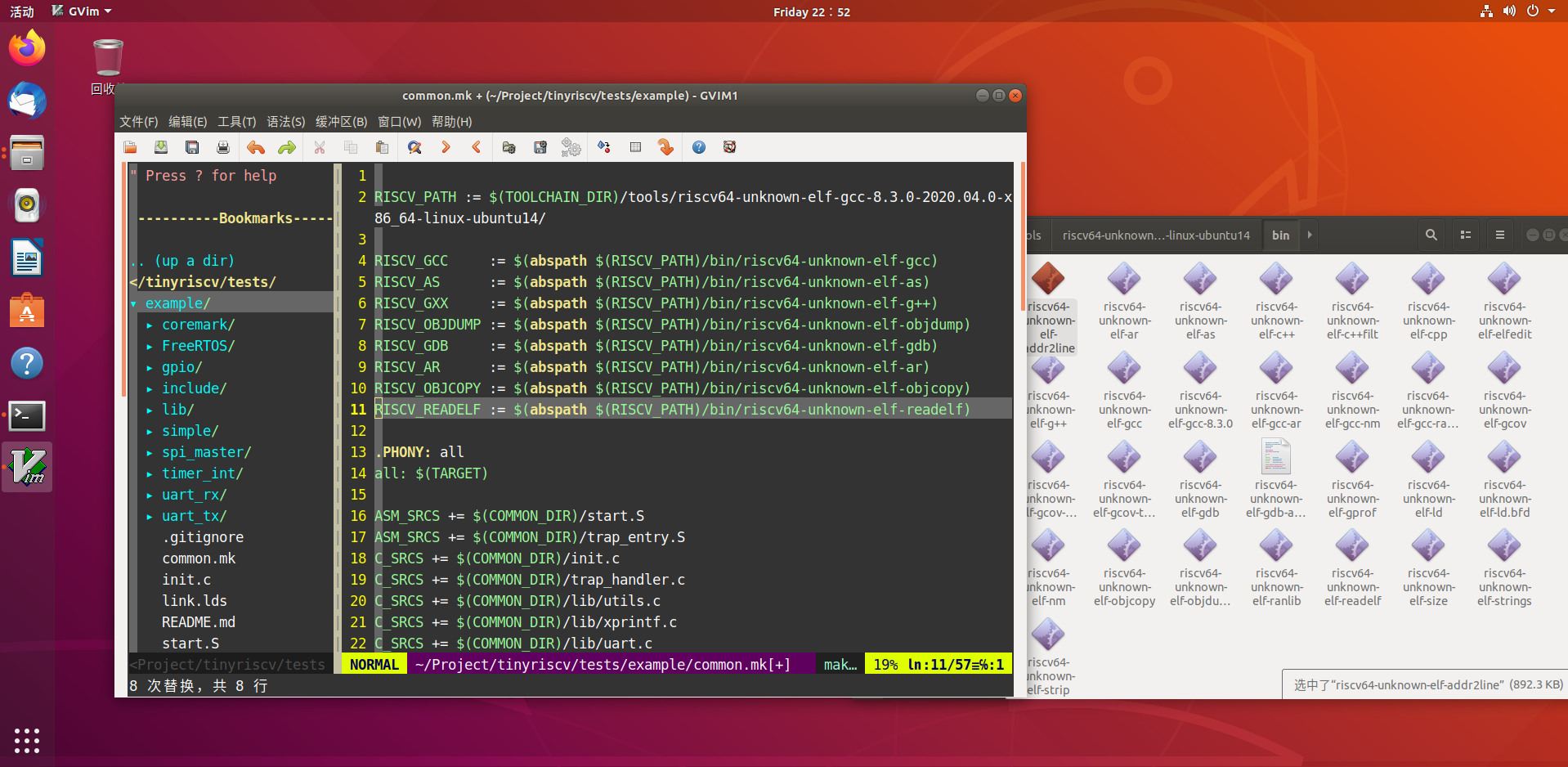

修改tinyriscv/tests/example目录下的common.mk文件

把名称修改过来,保持和工具链名称前缀一致。

:wq保存并退出

下面开始进行测试

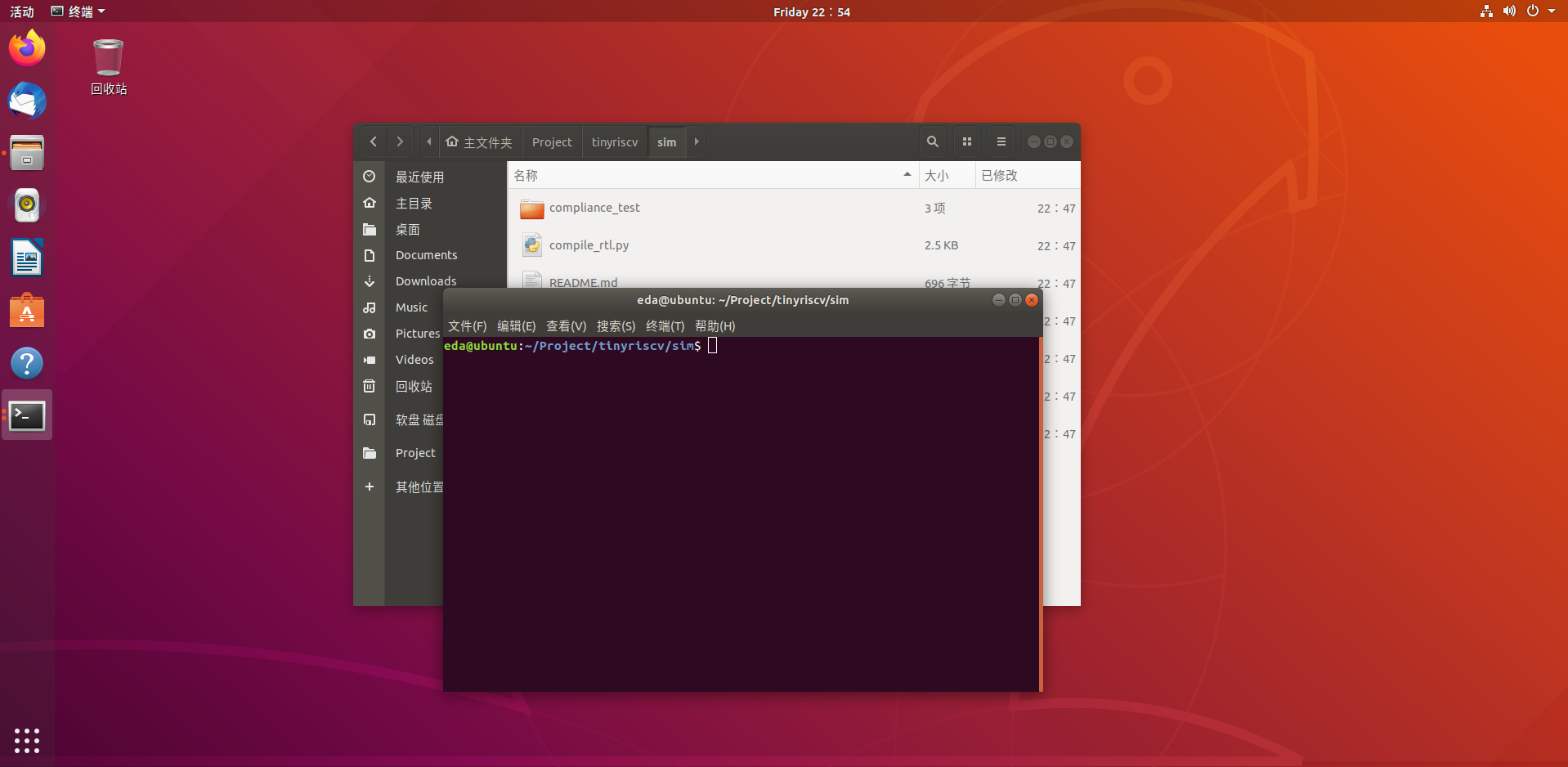

sim目录下启用终端

1 | |

指令执行会报错,说没有这个文件或目录。

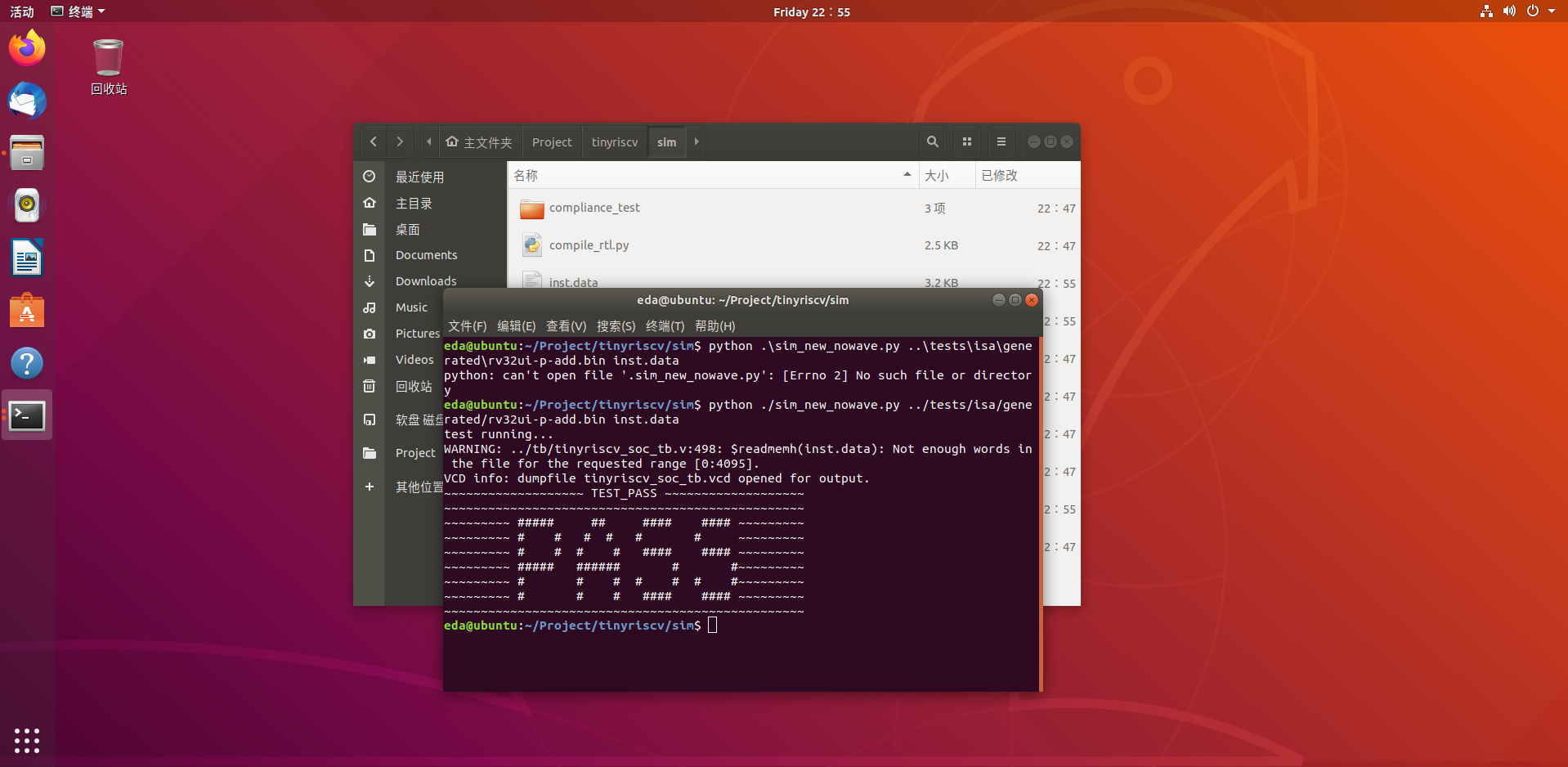

把右下划线全部替换为左下划

1 | |

顺利运行得到结果。

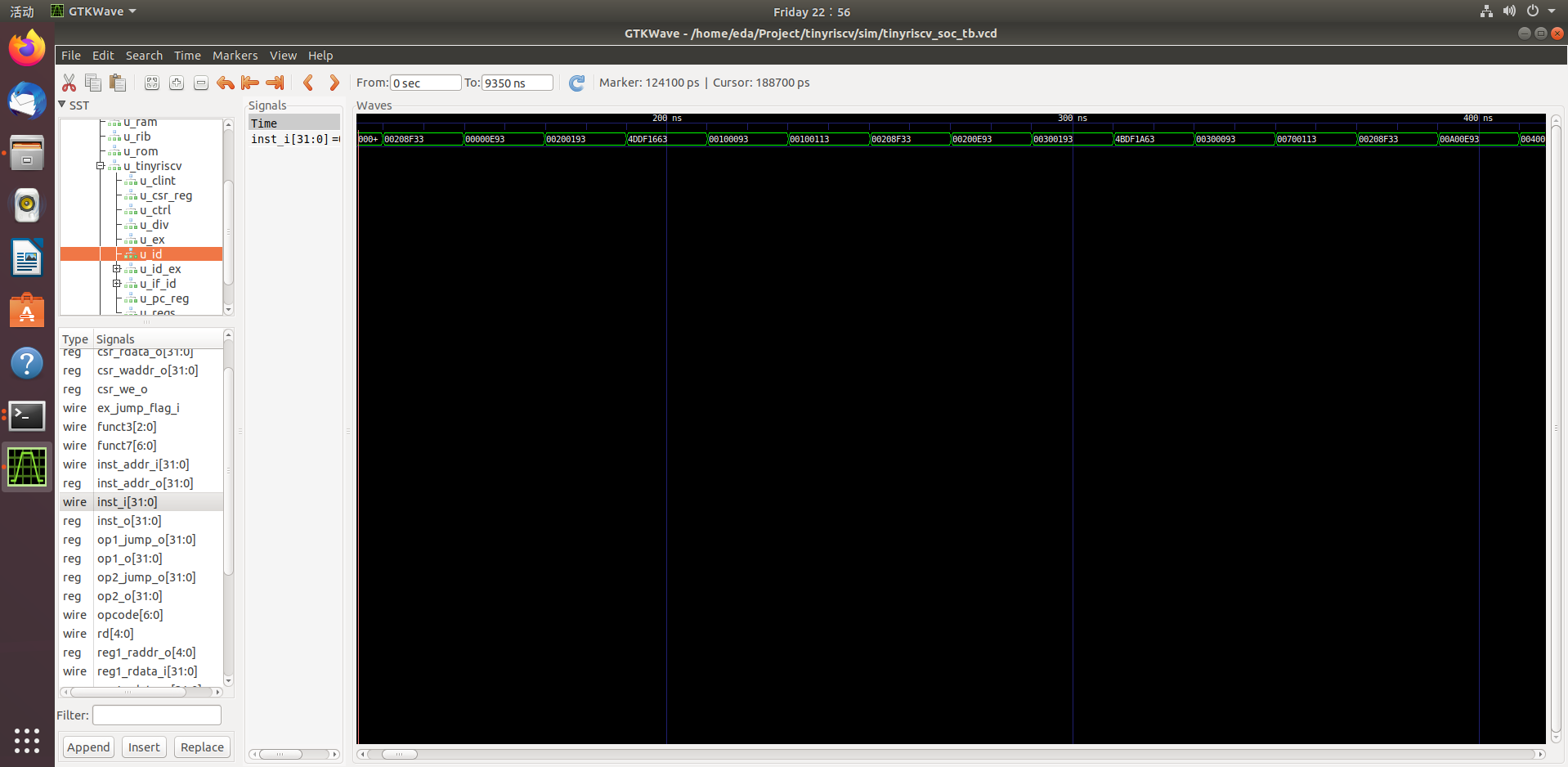

找到当前目录下的tinyriscv_soc_tb.vcd文件双击启动gtkwave查看

基本使用没有问题。

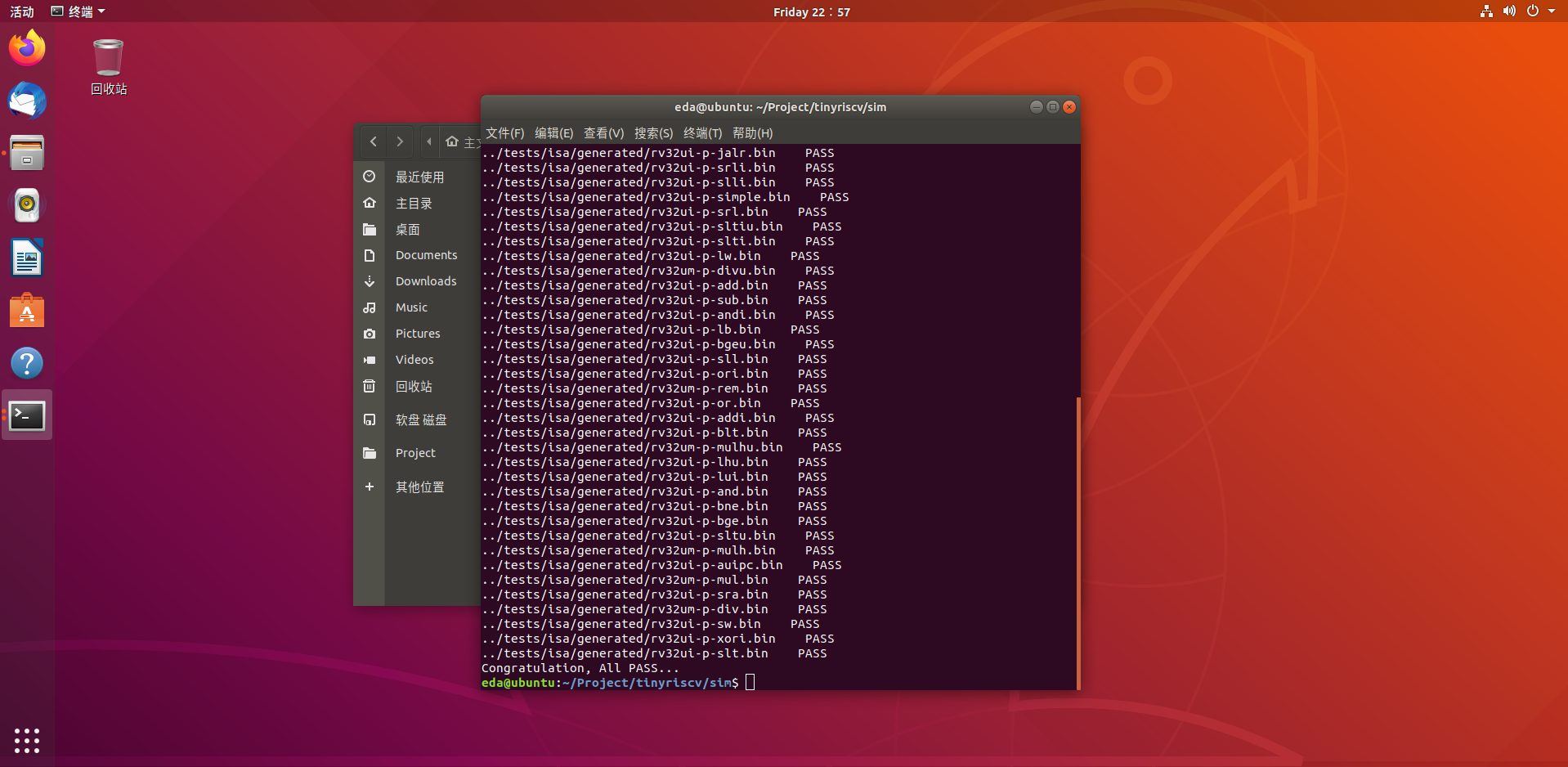

测试所有指令集

1 | |

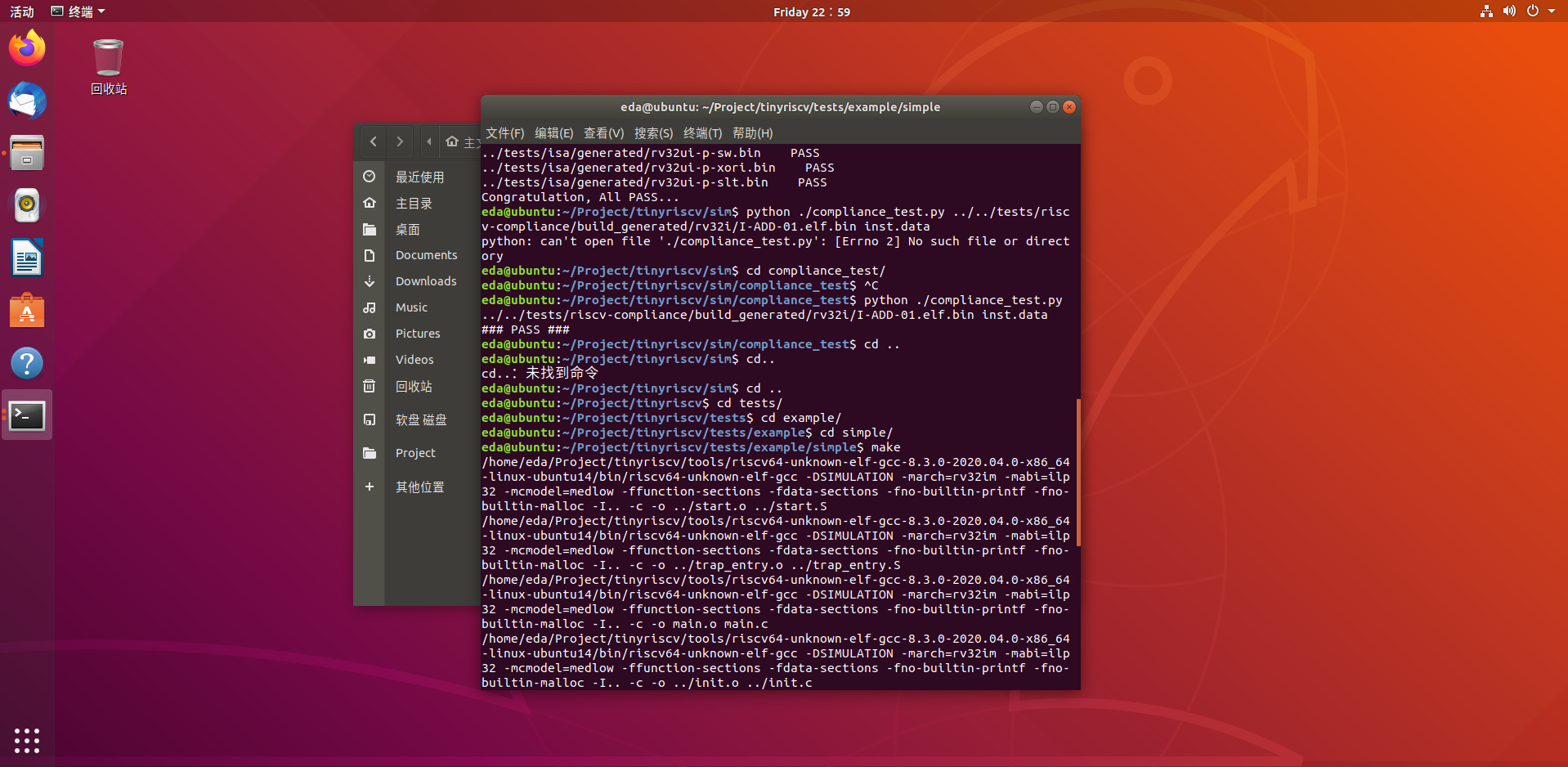

测试新指令集

进入到sim/compliance_test目录,执行以下命令:

cd compliance_test

python ./compliance_test.py ../../tests/riscv-compliance/build_generated/rv32i/I-ADD-01.elf.bin inst.data

得到PASS表明通过。

接下来测试c文件编译

进入到tests\example\simple目录,执行以下命令编译:

make

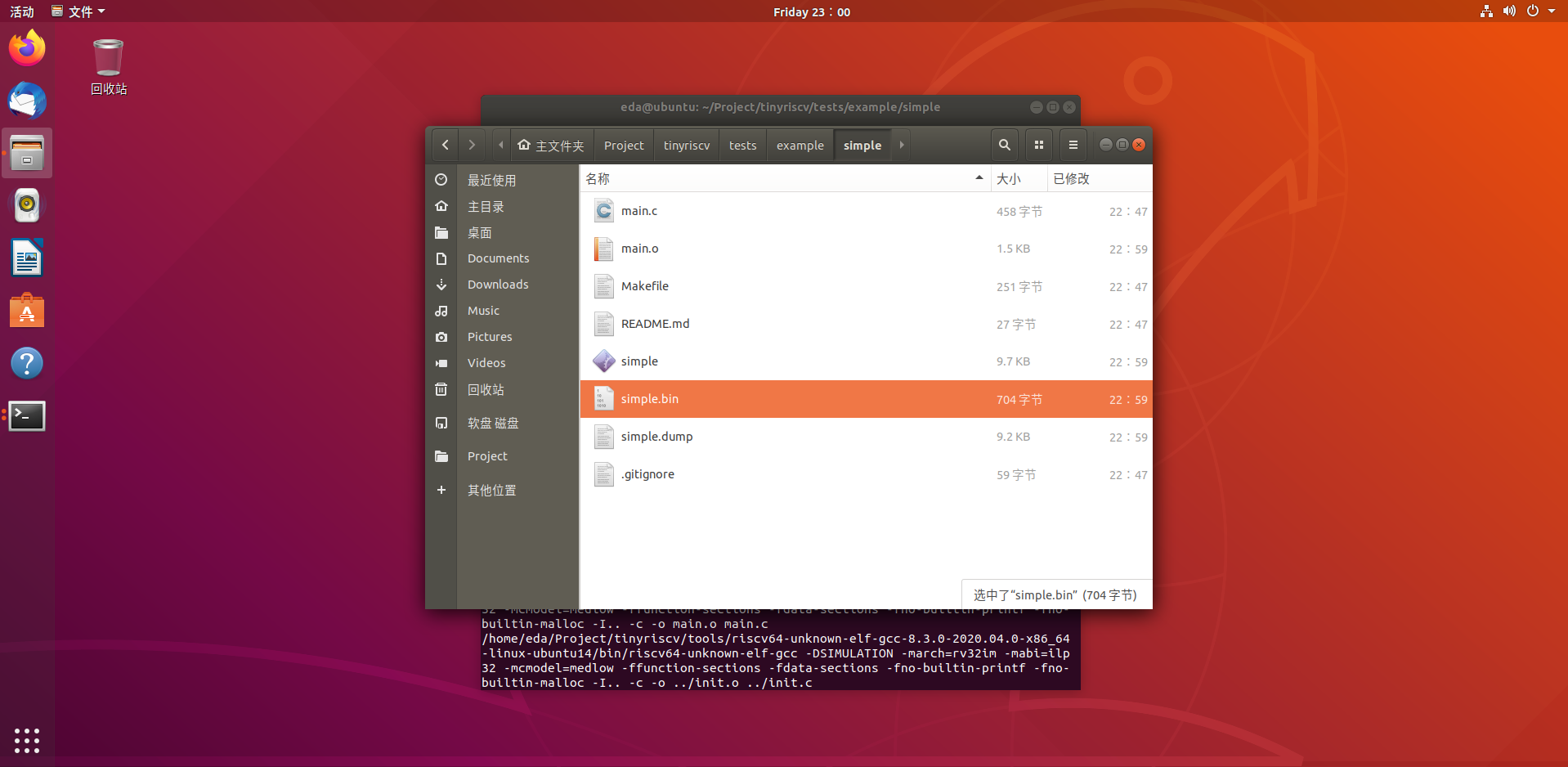

在该目录下回生成.bin文件

编译成功之后,进入到sim目录,执行以下命令开始测试:

python ./sim_new_nowave.py ../tests/example/simple/simple.bin inst.data

通过,那么至此基本仿真已经没有问题了。

下面测试FPGA移植。

FPGA移植准备

移植需要准备vivado集成开发环境和FPGA,CMSIS-DAP调试器。

我这里安装的是vivado2017.4和Digilent 的 ARTY A7 35T开发板

安装vivado需要准备安装包和许可文件,请自行准备。

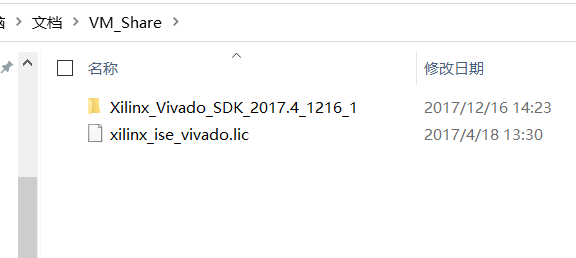

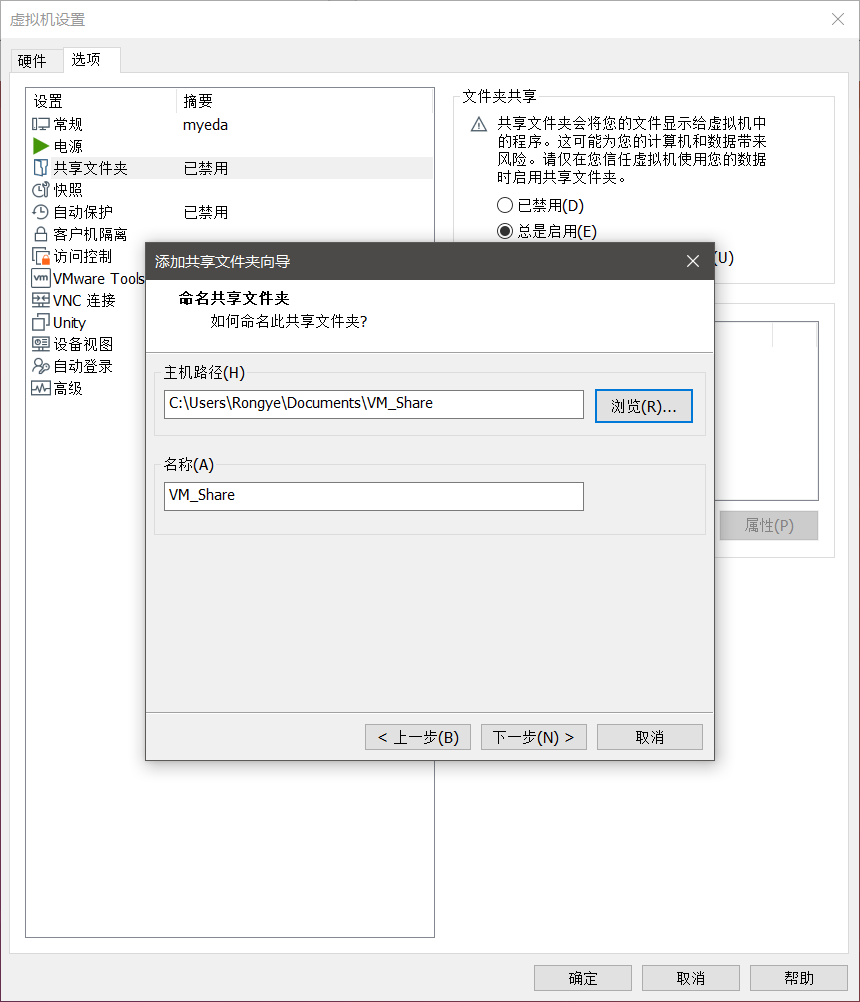

此处不能拖拽进虚拟机,需要利用共享文件夹的方式。

在虚拟机设置中,将USB兼容性先修改为USB 3.1

切换到“选项”

启用共享文件夹,不需要关机。

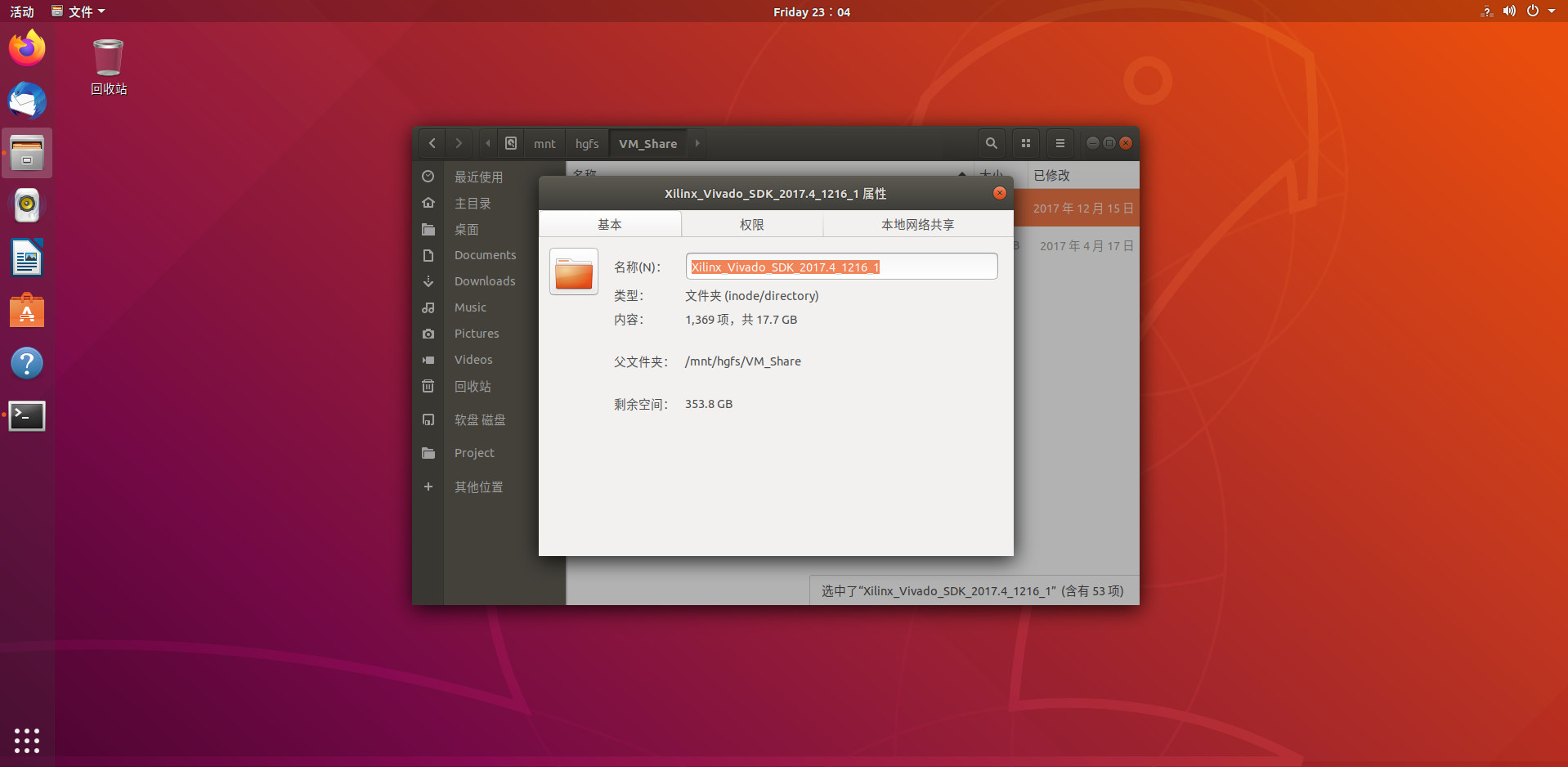

之后在根目录/mnt/hgfs/就可以找到自己的共享文件夹了。

进入安装包文件夹,

赋予安装权限

chmod +x xsetup

执行命令

./xsetup

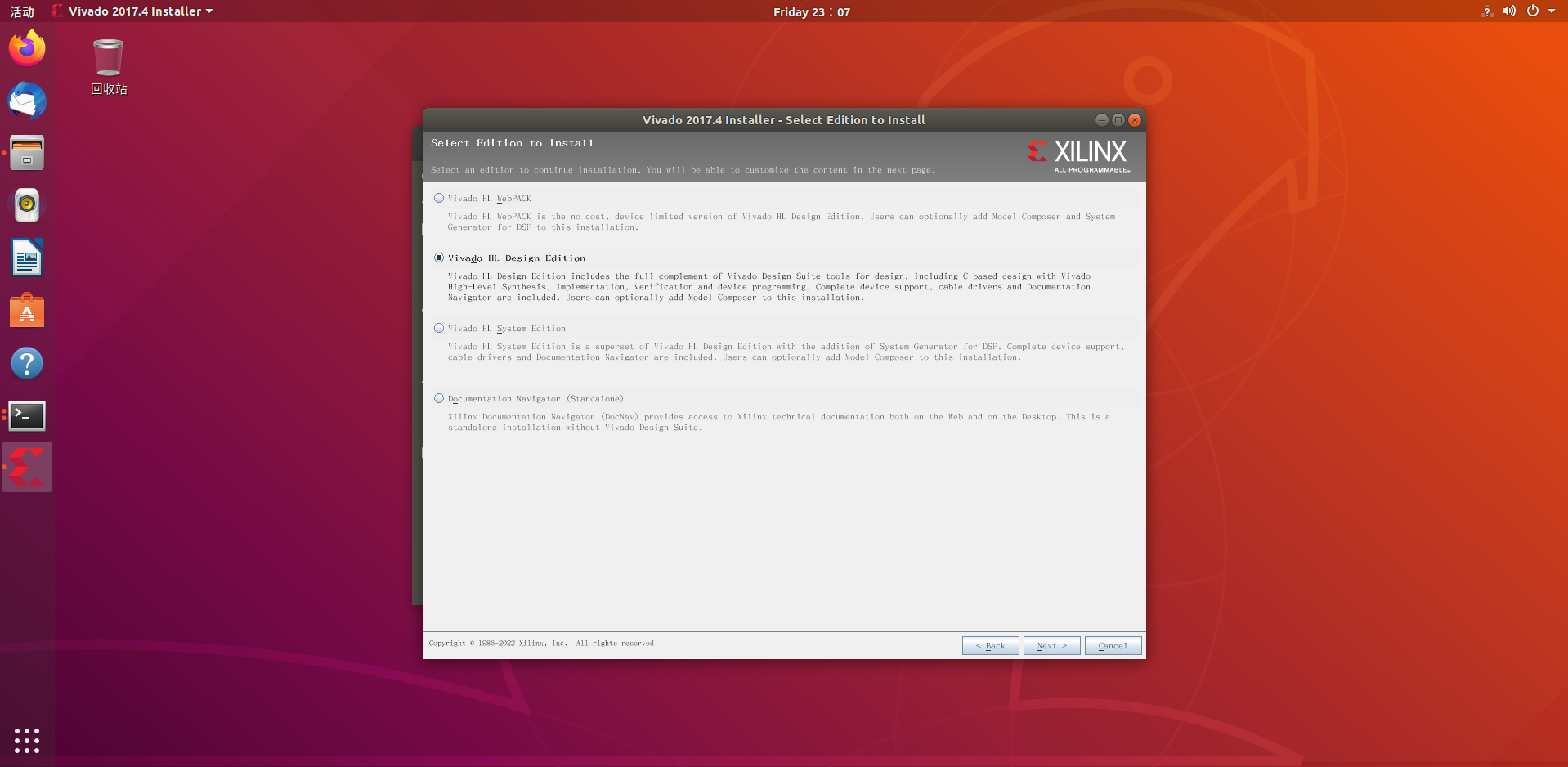

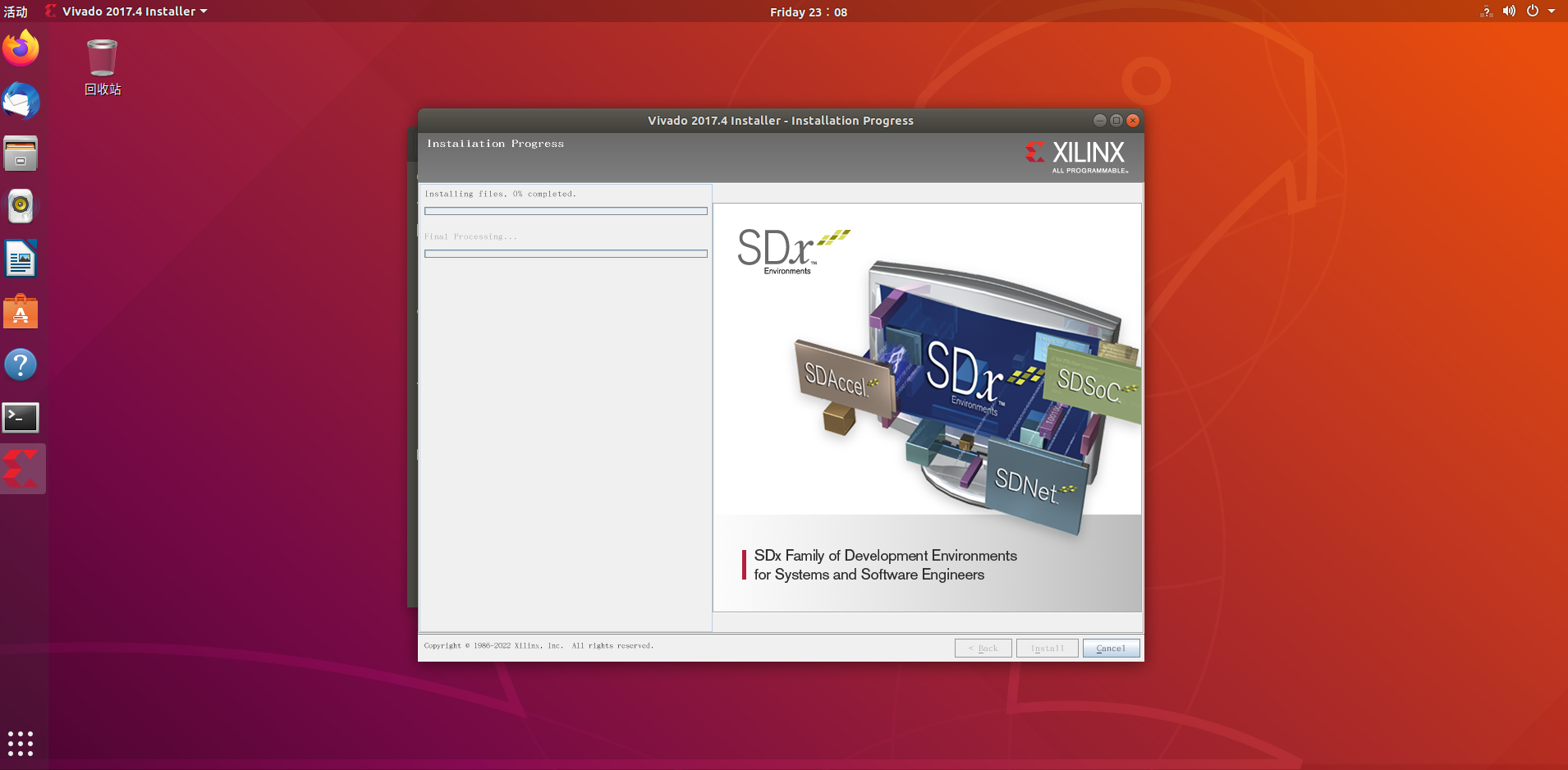

启动安装引导

安装过程和windows下没有区别。

安装路径要在/home下,不然空间不足。此处建立了一个EDA_Tools目录供后续各种工具安装。

安装末尾载入许可文件。

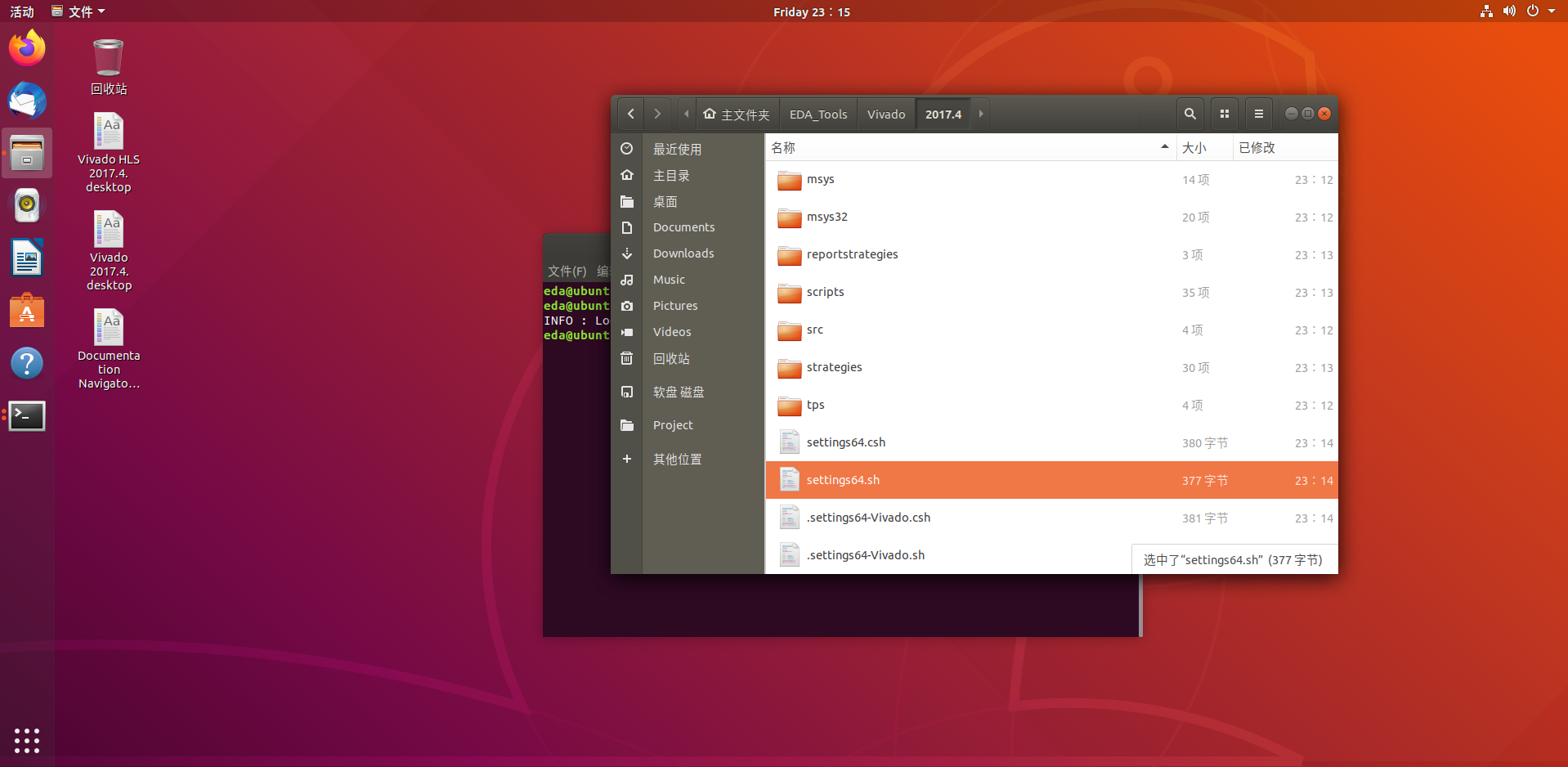

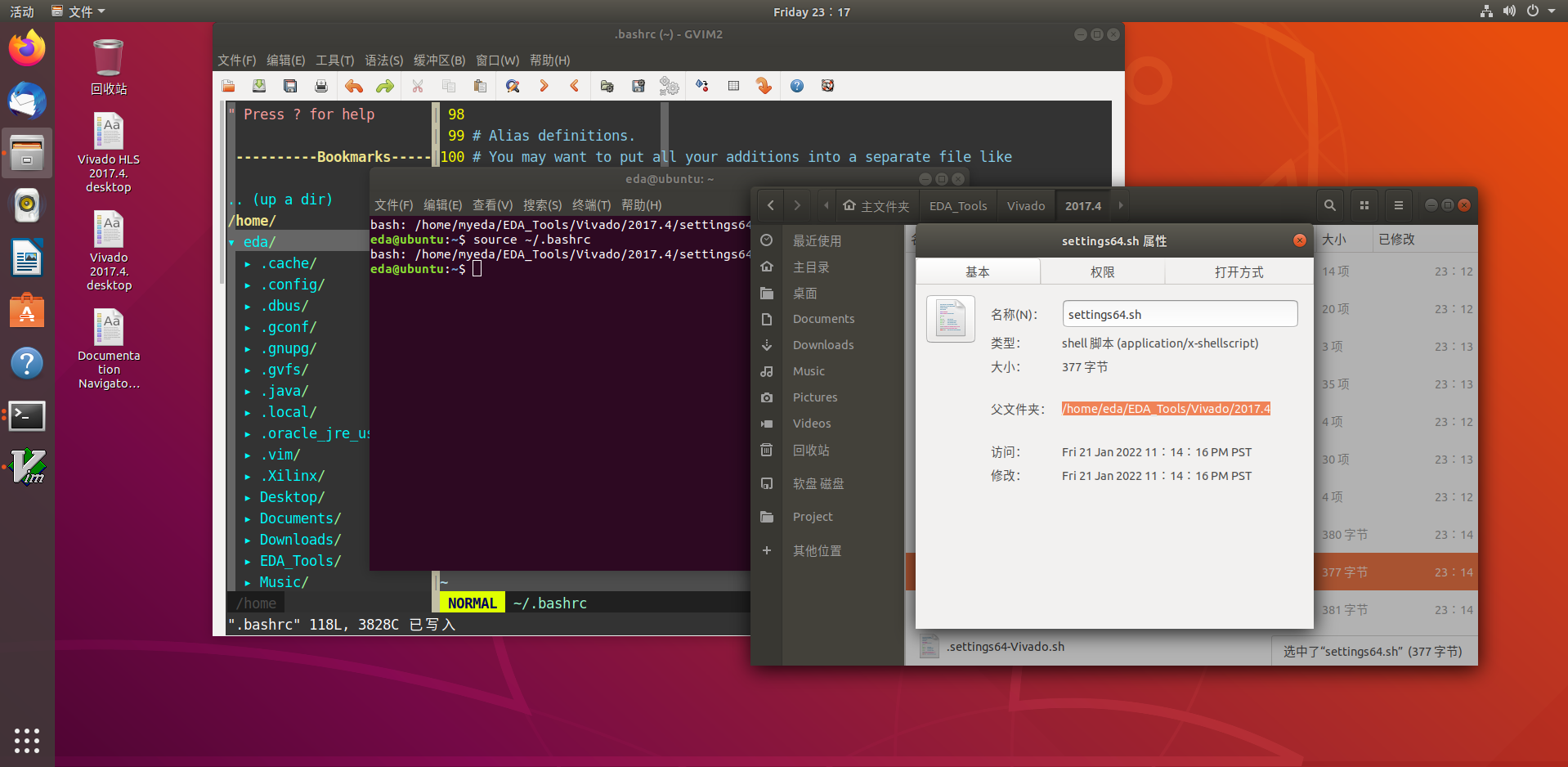

在vivado/2017.4目录下找到settings64.sh配置文件。

编辑主目录配置文件

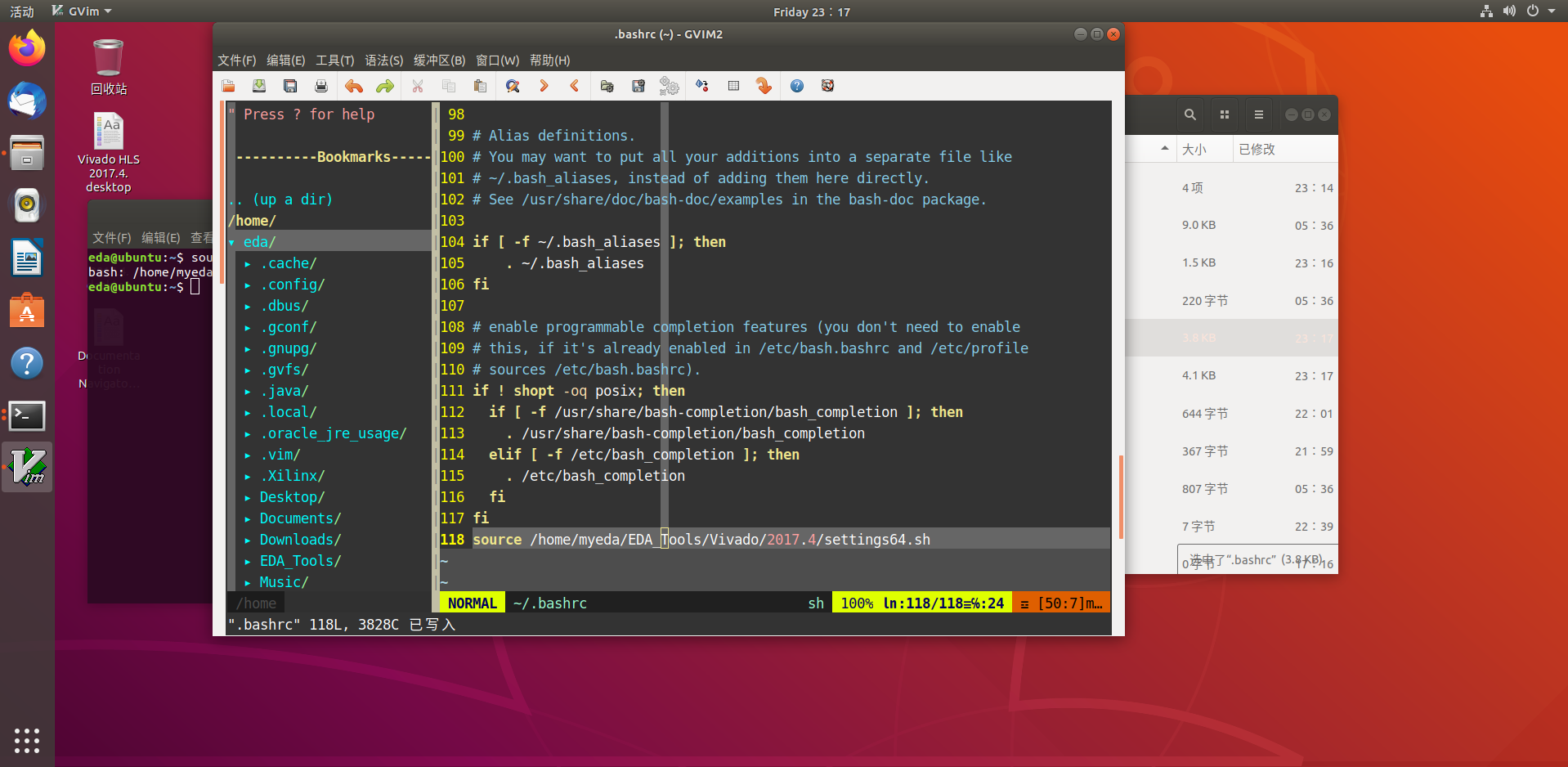

vim ~/.bashrc

在末尾添加路径

source /home/eda/EDA_Tools/Vivado/2017.4/settings64.sh

然后重新加载环境配置

source ~/.bashrc

至此应该就可以启动vivado了。

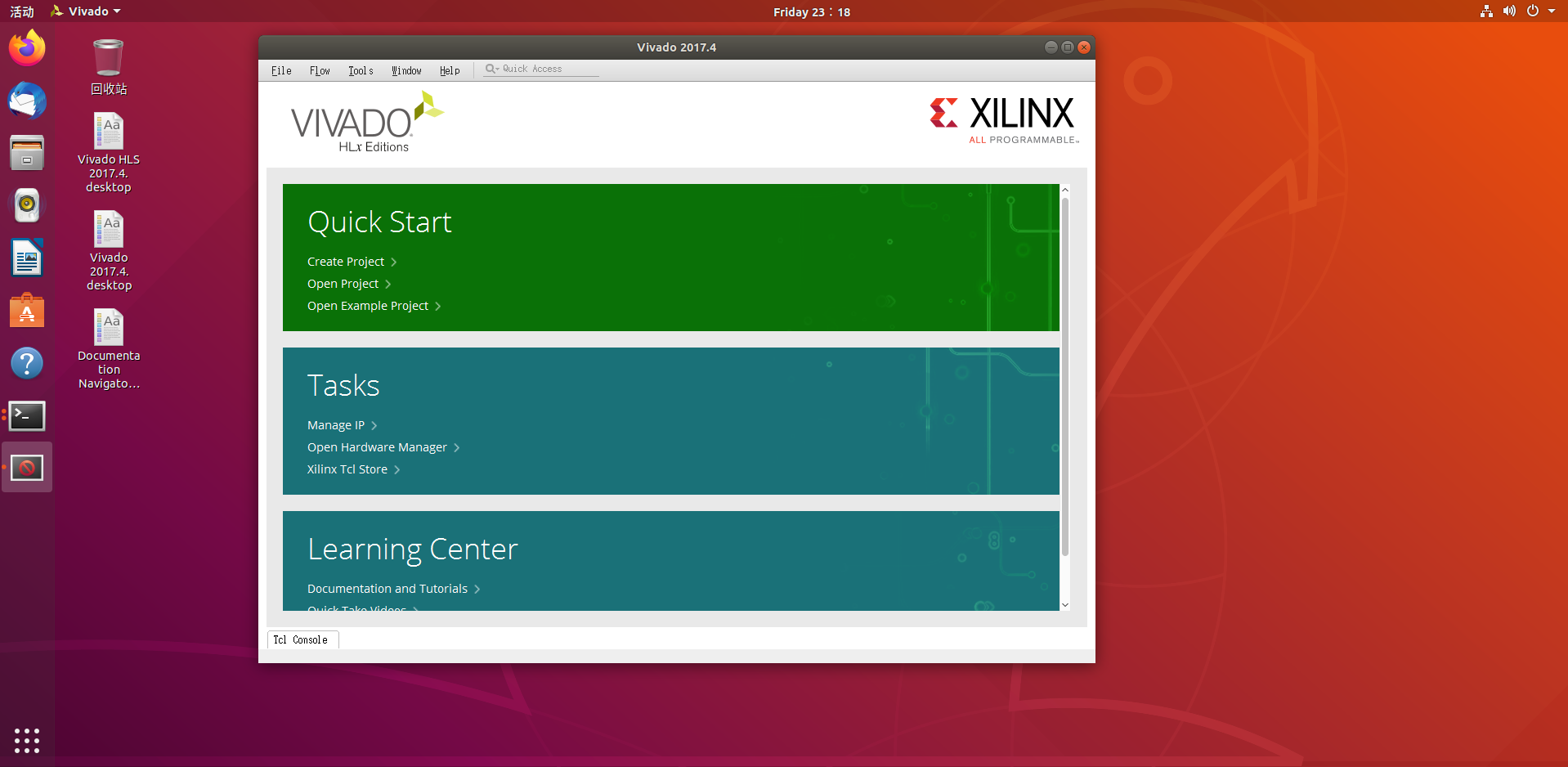

vivado &

启动vivado

顺利启动以后先关闭,处理一些剩余内容。

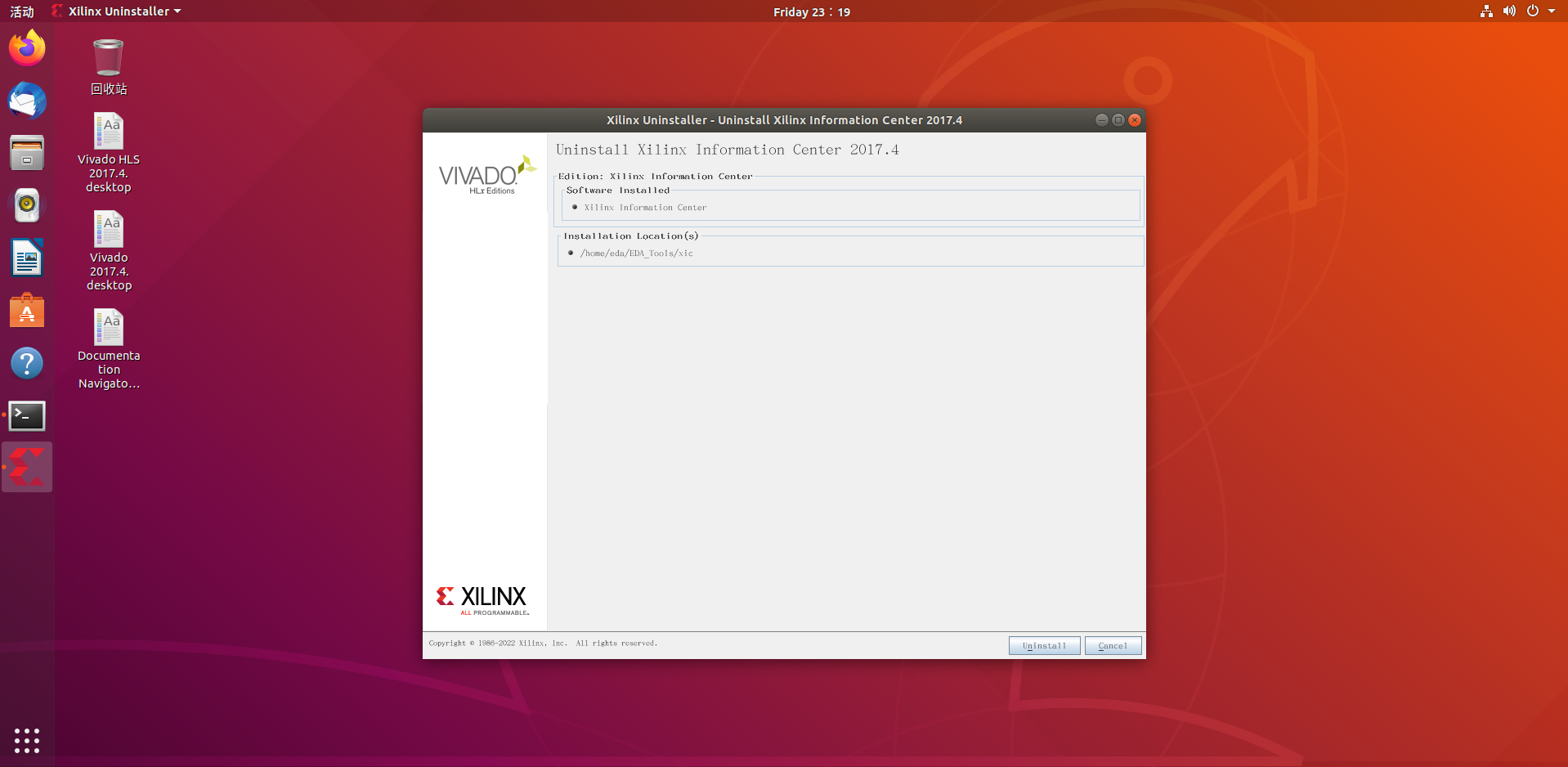

先把xilinx的信息中心卸载掉。

找到这个软件,打开。

直接卸载就行。

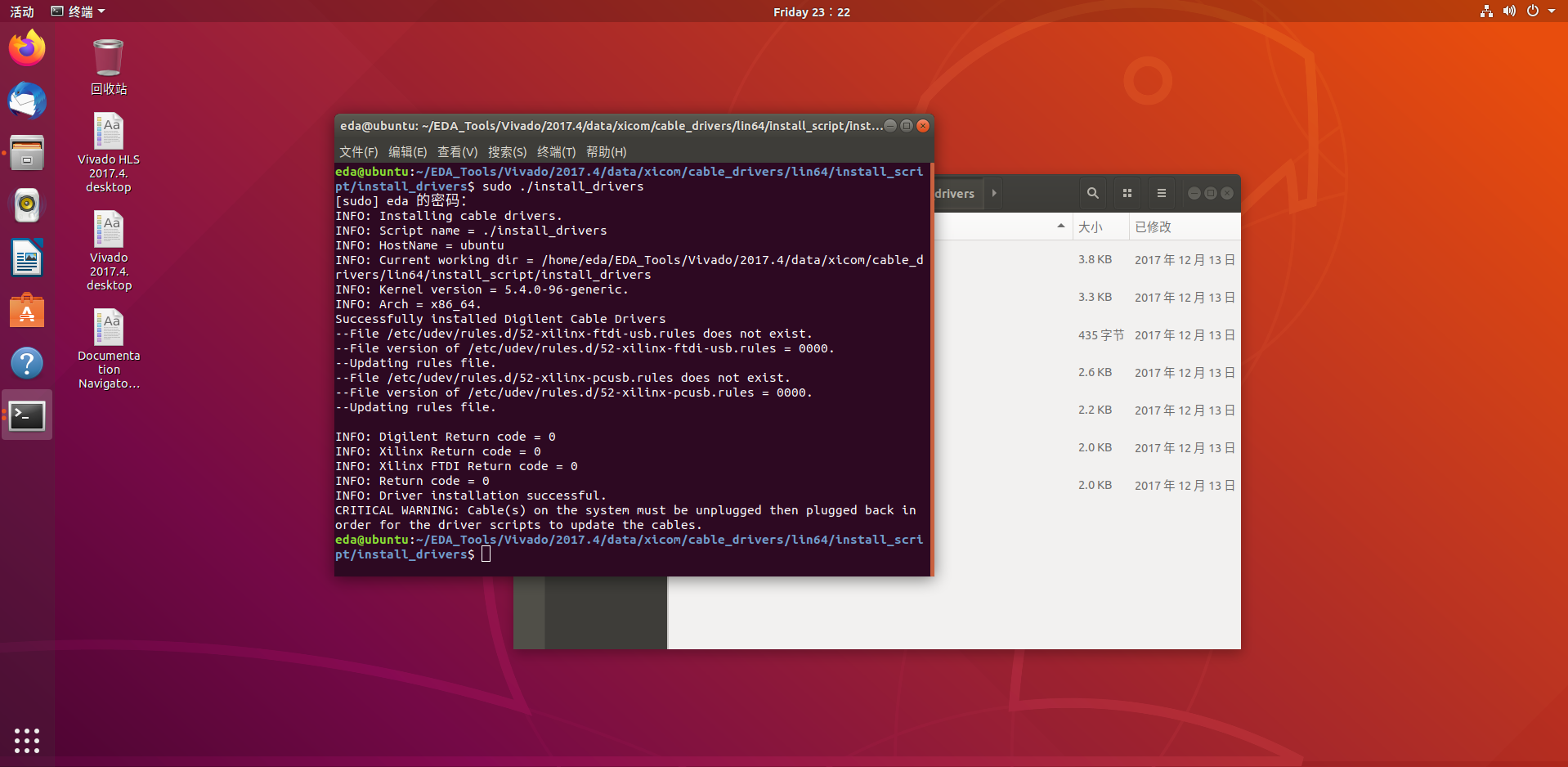

接着补充安装驱动,否则后续可能无法烧写板子。

/home/eda/EDA_Tools/Vivado/2017.4/data/xicom/cable_drivers/lin64/install_script/install_drivers

在这个路径下,打开终端。

安装驱动。

sudo ./install_drivers

那么vivado也准备完毕以后,开始移植tinyriscv到FPGA上

FPGA移植工作

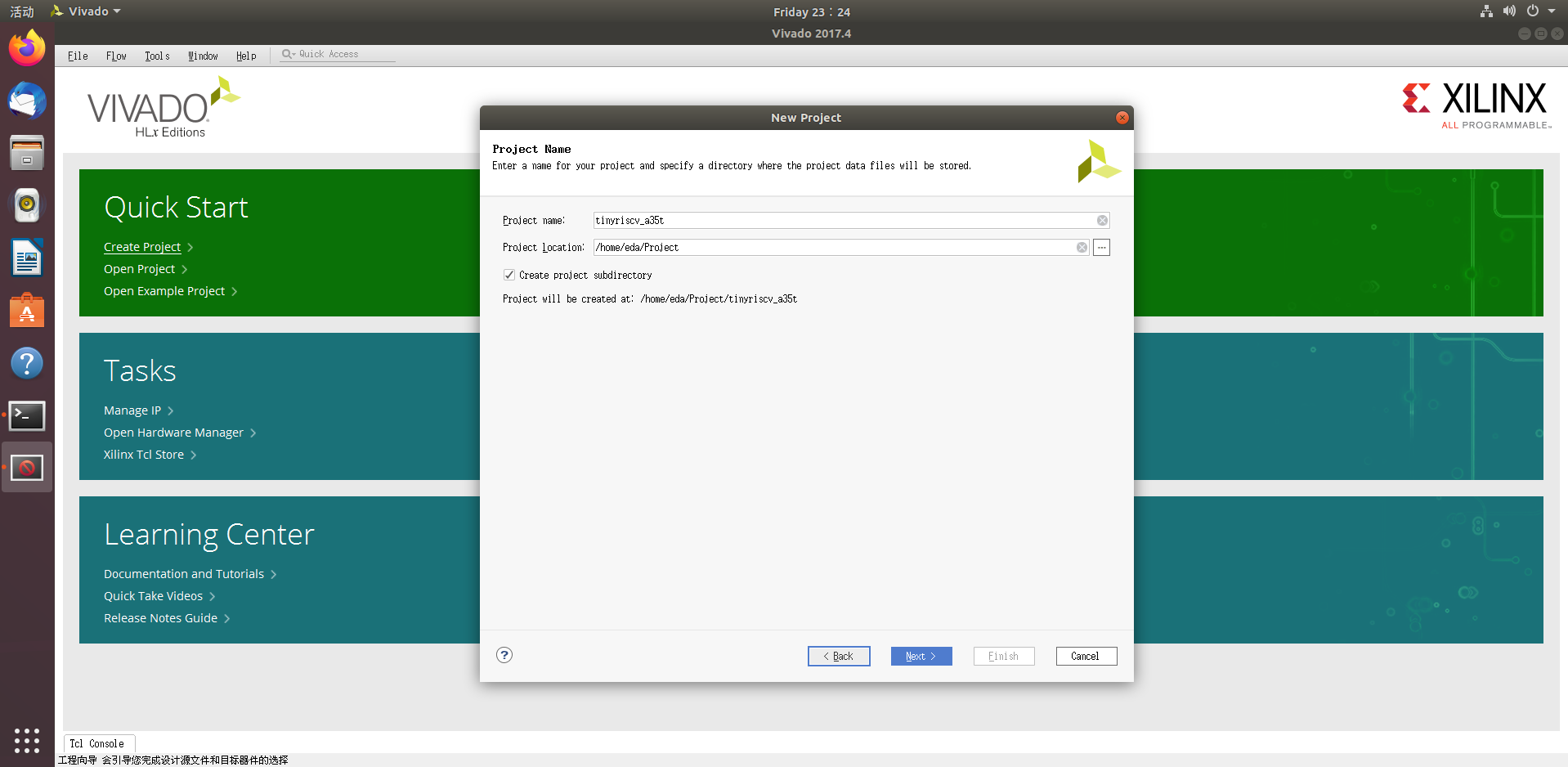

新建工程

我的板子ARTY A7 35T

器件属性选择xc7a35ticsg324-1l

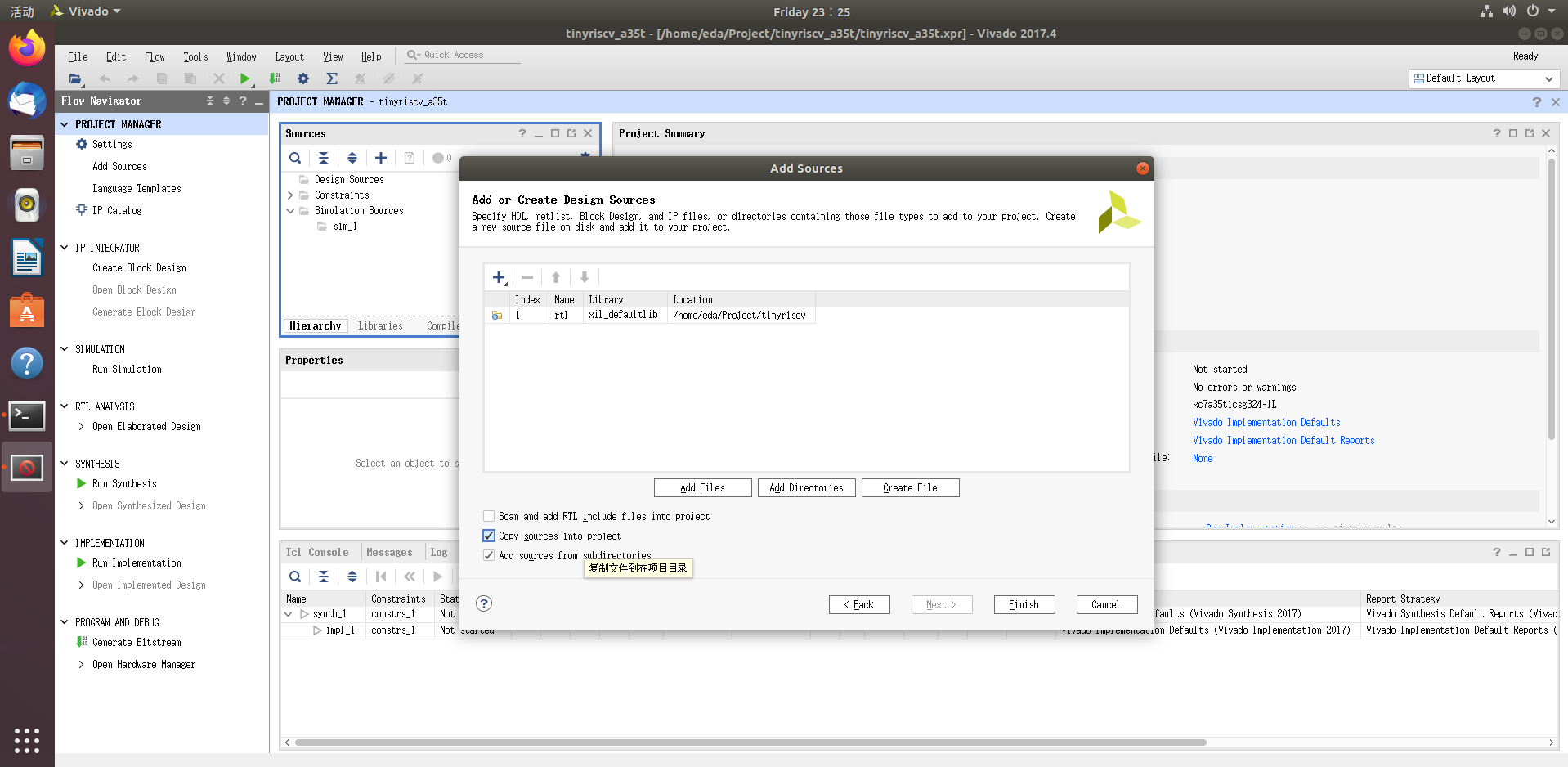

添加源文件

将tinyriscv下整个RTL添加复制进来

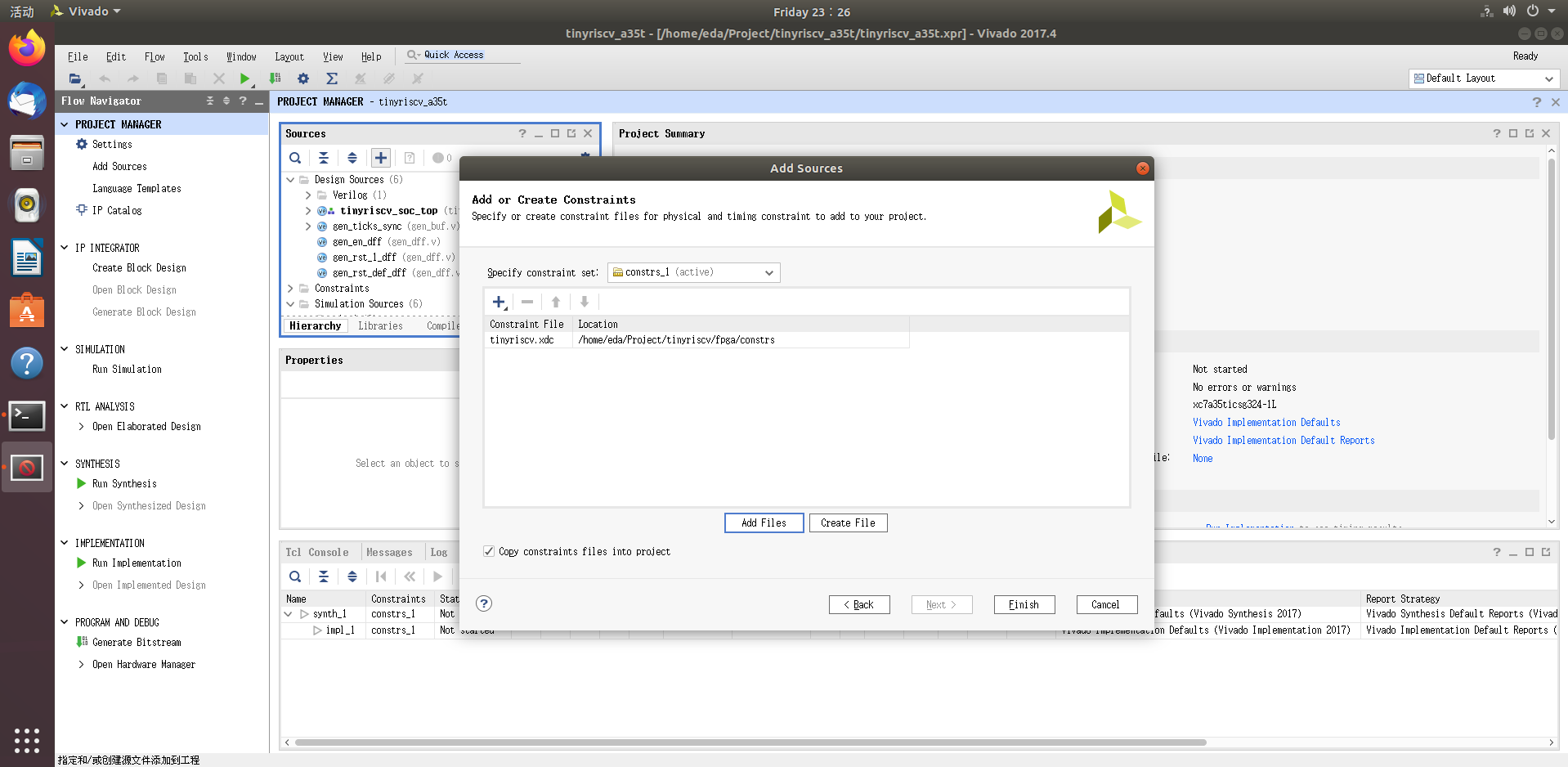

将tinyriscv下fpga/constrs下的.xdc约束文件添加进来。

打开约束文件,根据自己的开发板进行修改。此处为我自己的约束。

重点关注时钟,我是100M的时钟,等会还要用PLL分频。

GPIO0,1。我分配给了一个LED和一个SW拨码开关。

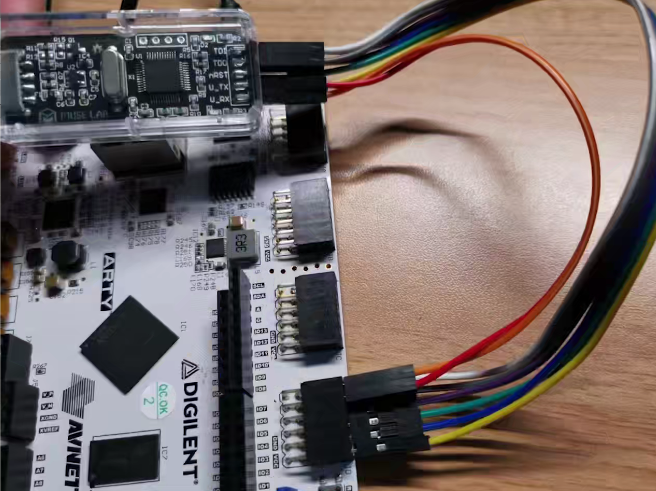

JTAG和UART使用调试器CMSIS-DAP的相应接口。

都根据自己开发板的原理图来。

1 | |

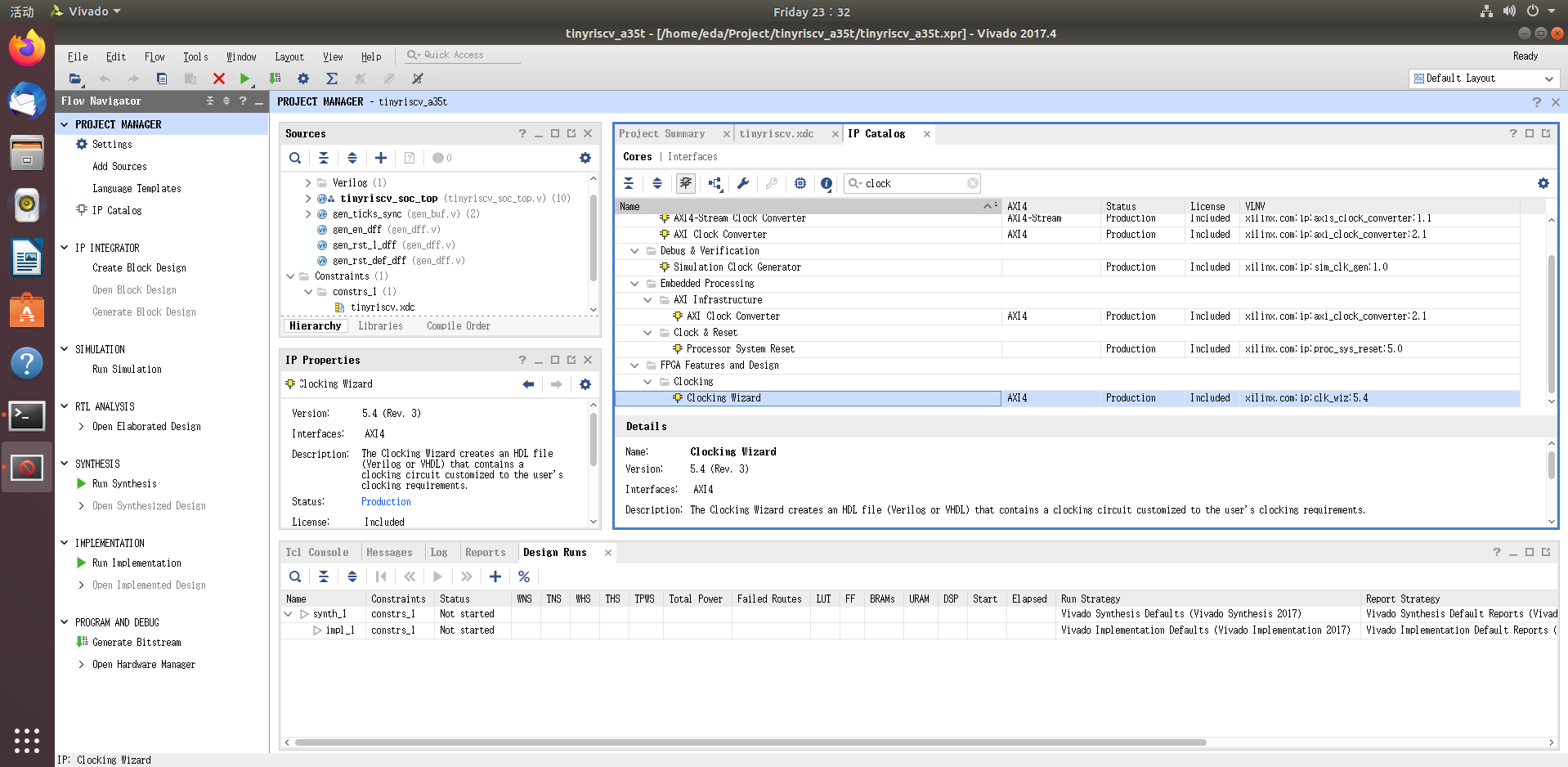

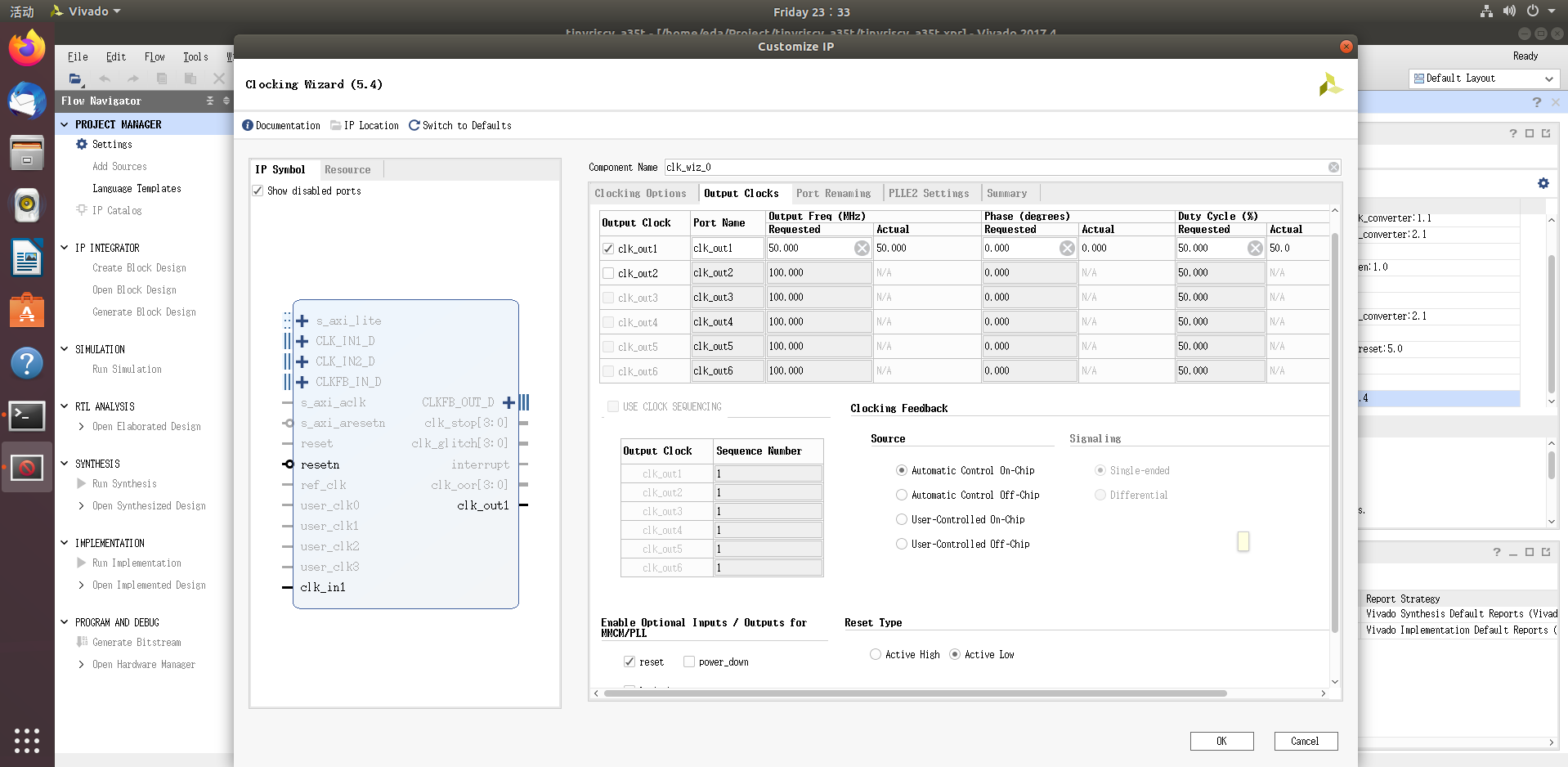

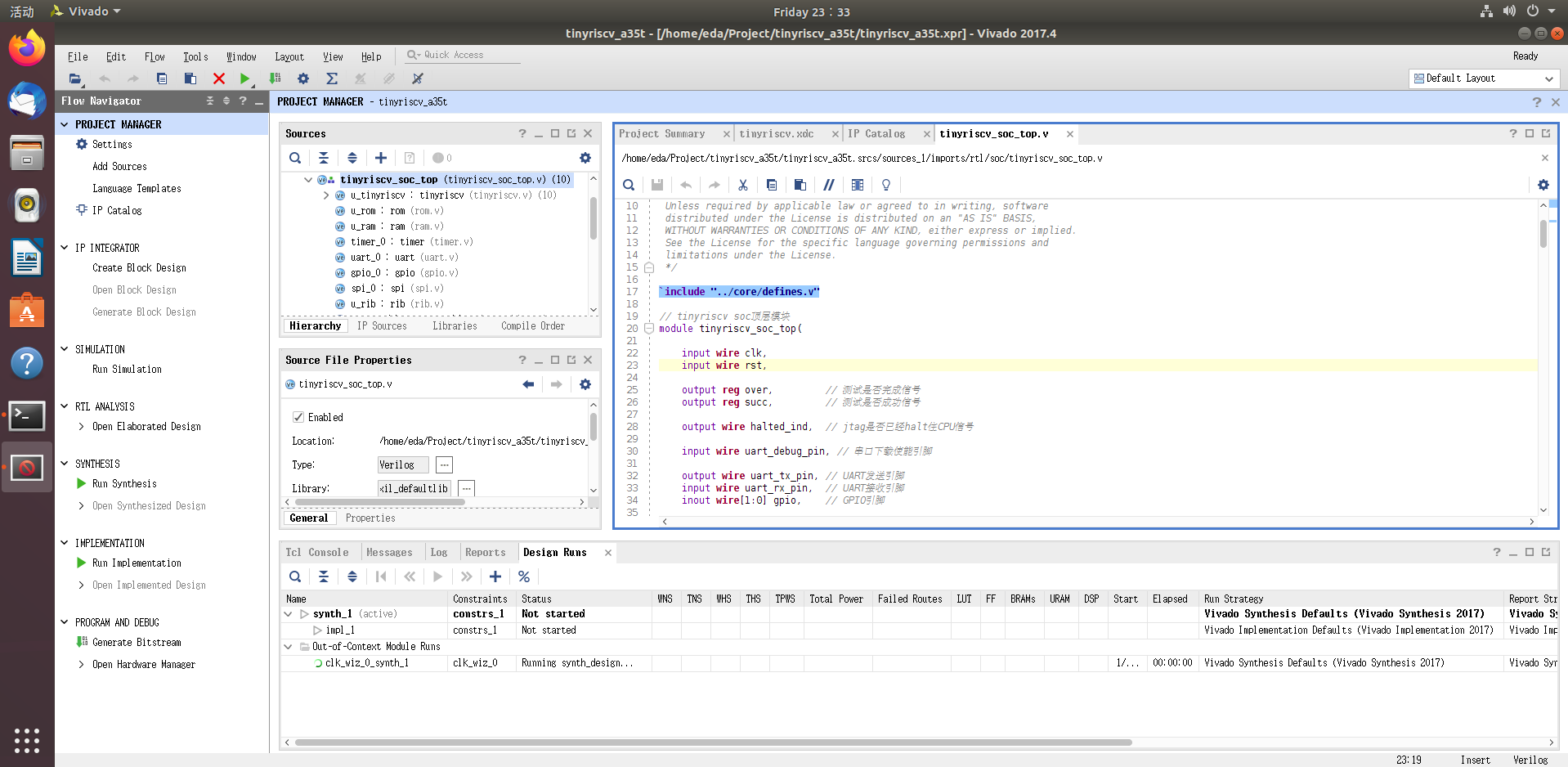

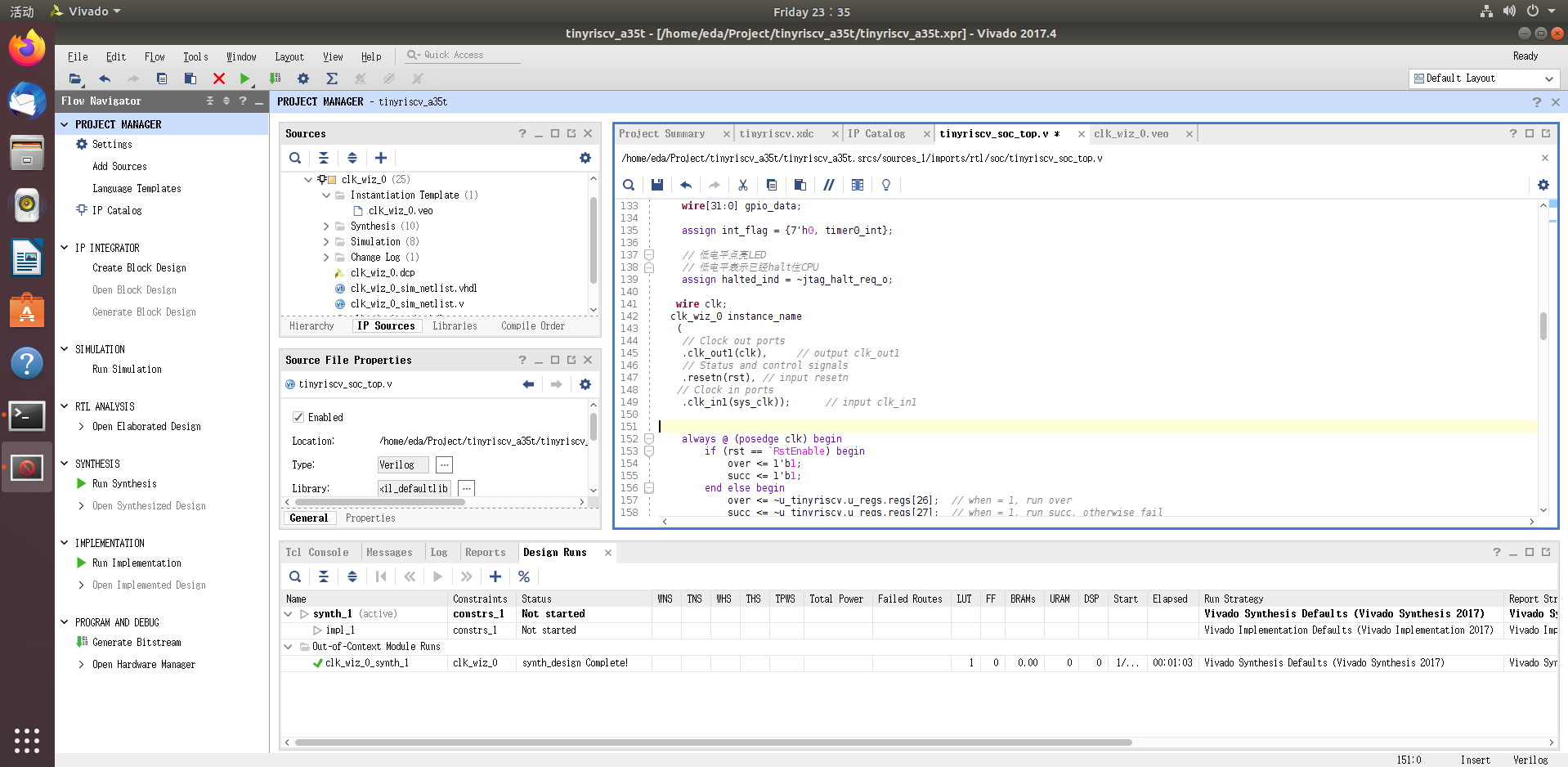

接下来添加锁相环PLL,

配置IP输出50M时钟

打开顶层文件,修改端口clk为sys_clk

往下,在第一个always块前例化PLL

记得补充声明clk,

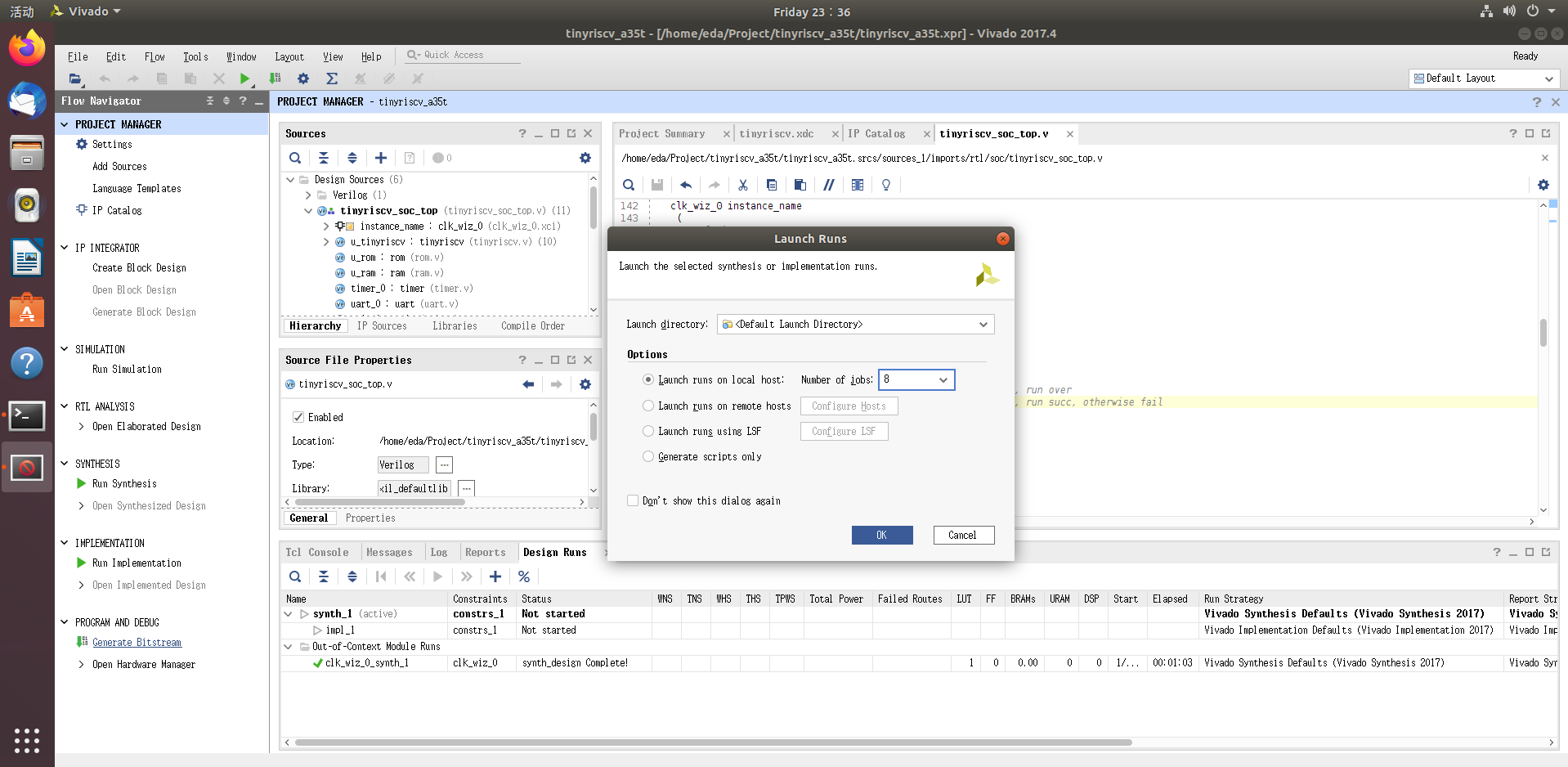

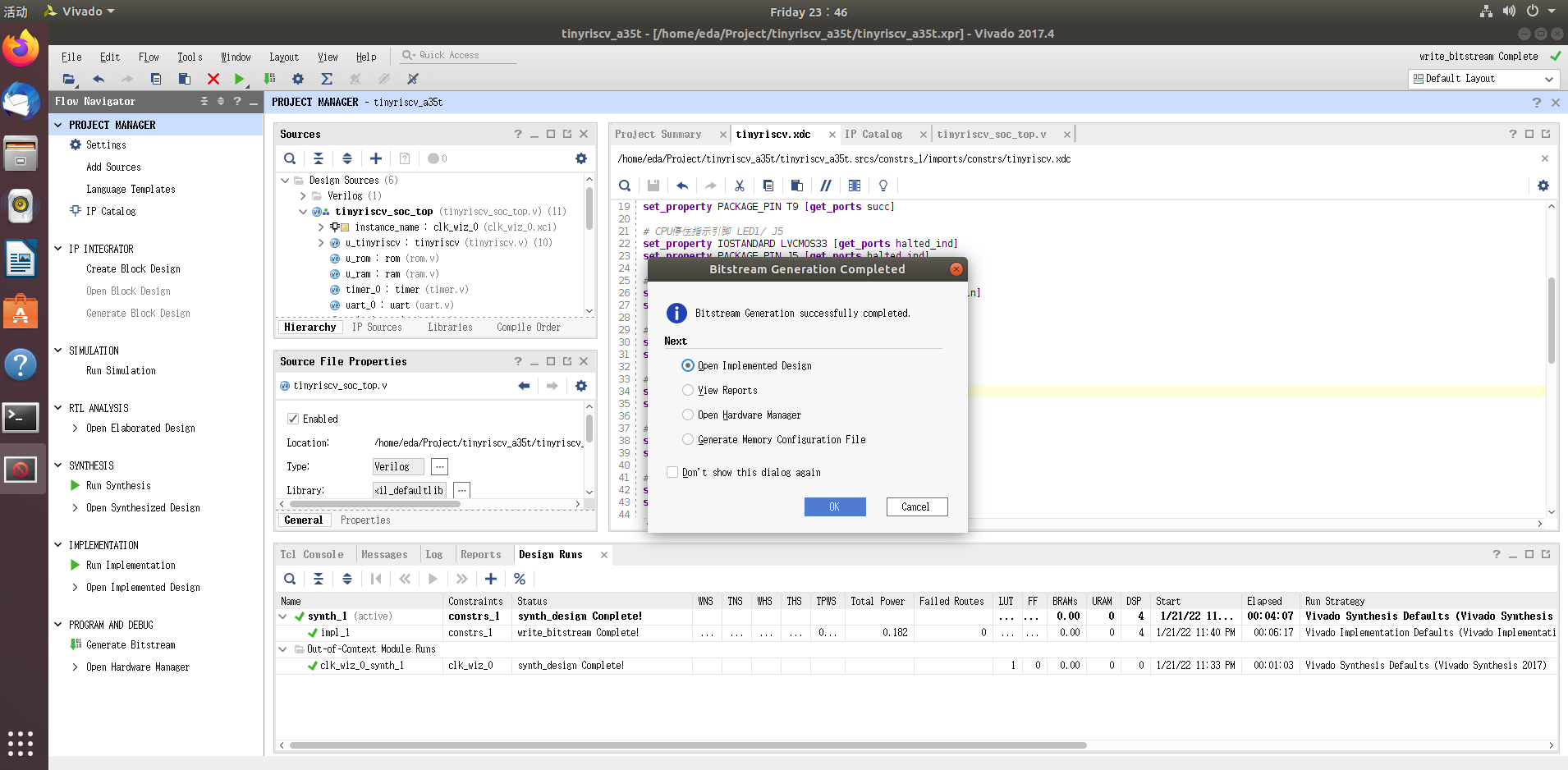

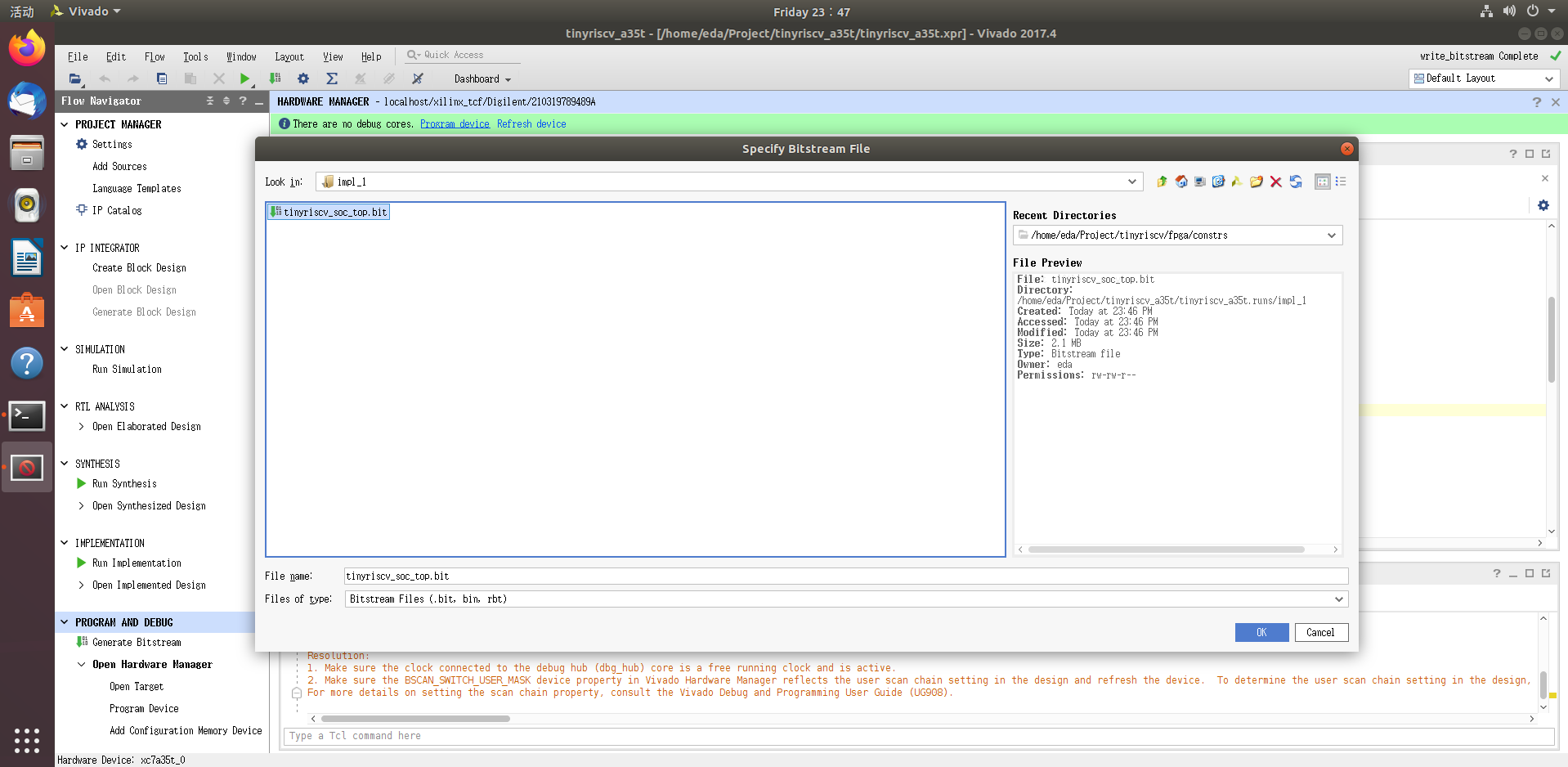

至此完成所有FPGA工程配置,生成比特流文件

顺利生成比特流文件,连接开发板直接烧写。

烧写时可能需要重新定位一下,自己生成的bit文件。

板子上的LED亮起,说明顺利烧写进去了,

接下来进行JTAG调试。

FPGA运行调试

调试需要使用到CMSIS-DAP,连好线,做好管脚约束才能使用。

同时还需要上位机,作者提供的只有exe也就是windows下的软件。

*注意,Linux下的openocd安装非常麻烦,我遇到了很多问题,虽然现在顺利安装并使用了。

不介意的话后续工作可以直接在windows上进行,把一些文件直接拖到windows下使用即可。

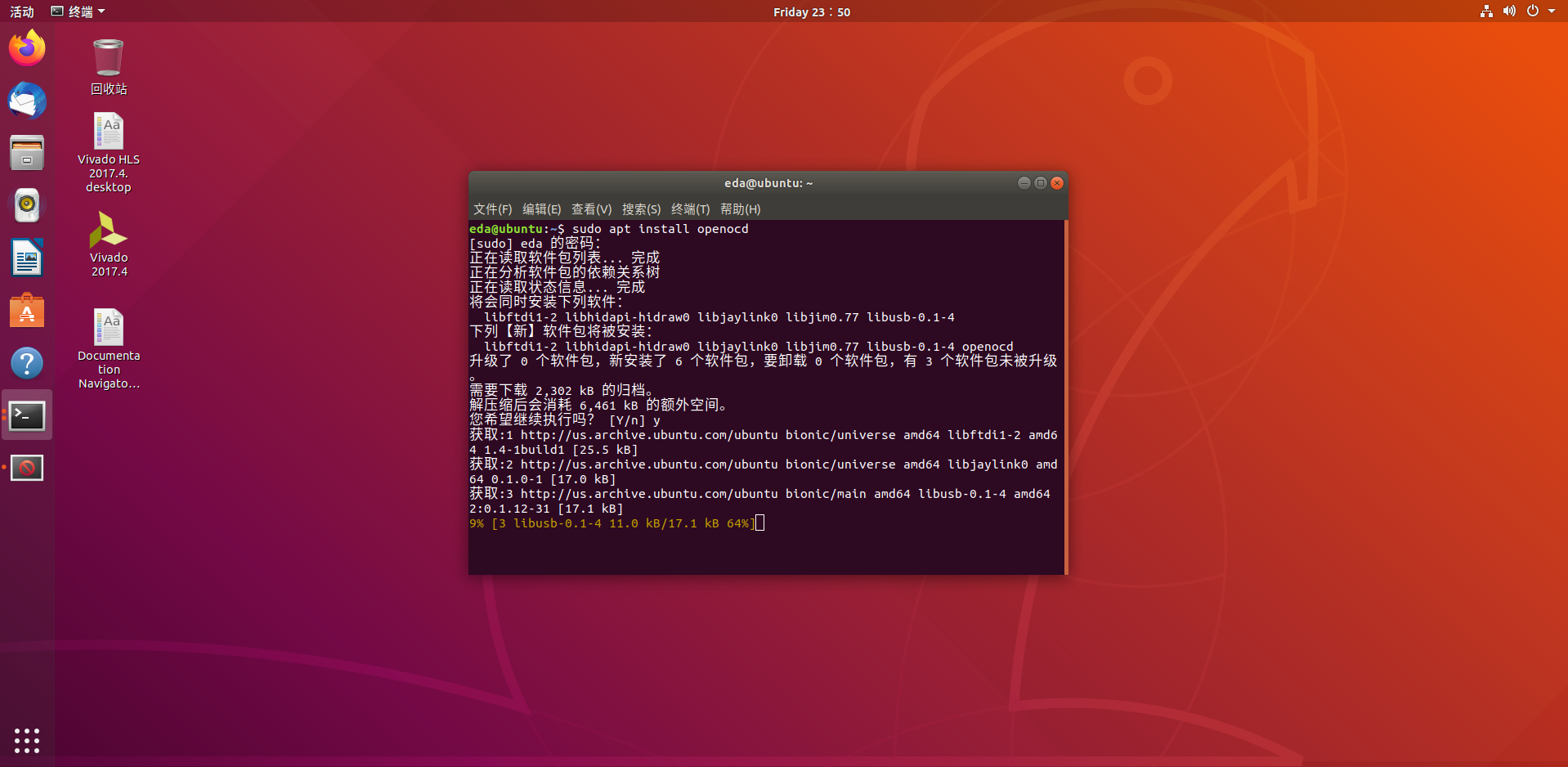

在Ubuntu下直接安装上位机openocd

sudo apt install openocd

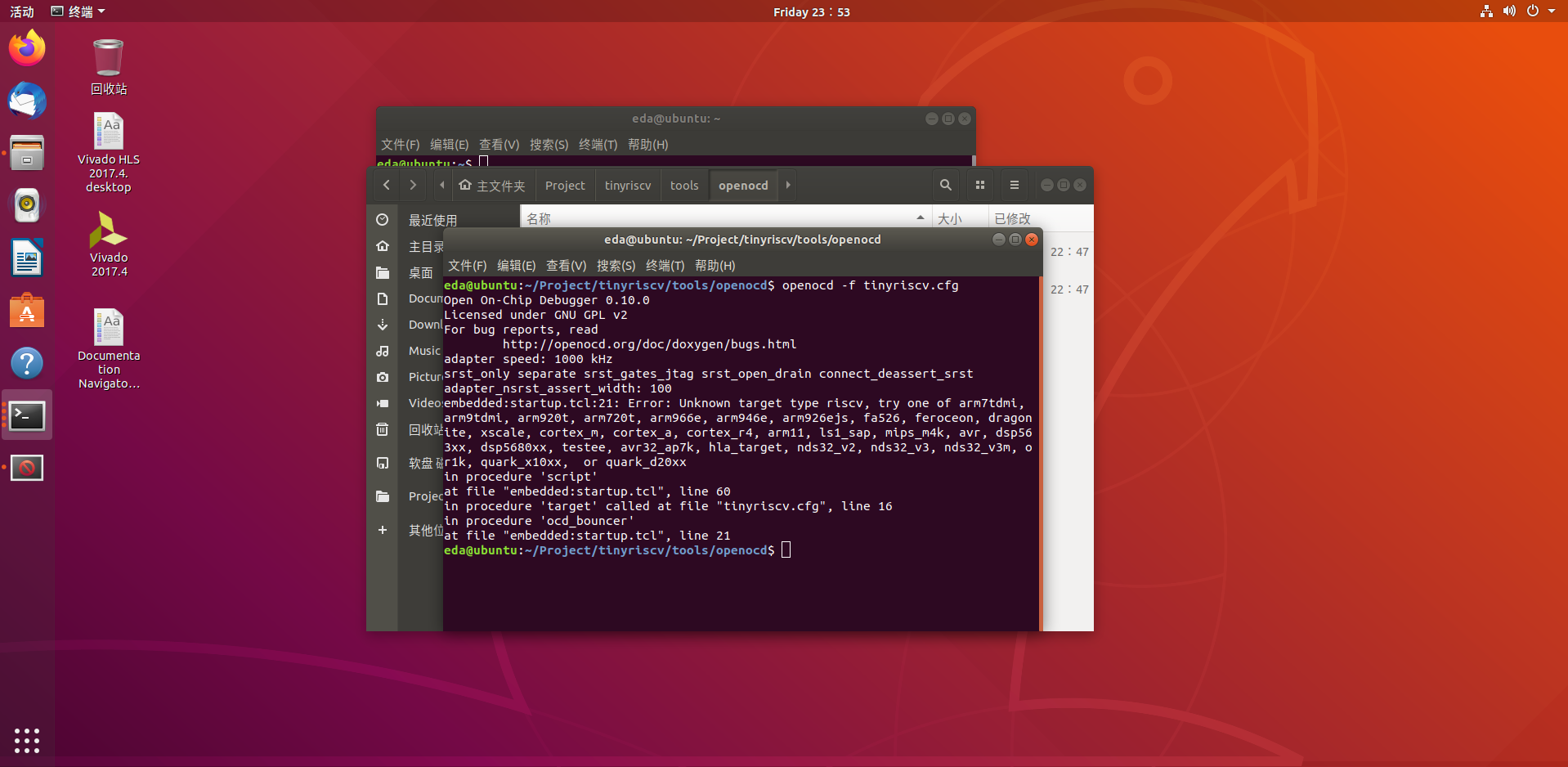

在tools/openocd目录下,我们需要使用到这个.cfg配置文件。

openocd -f tinyriscv.cfg

提示不行,这是因为默认安装的openocd不支持CMSIS-DAP,

所以我们还需要源码安装自己配置

sudo apt remove openocd先卸载掉原本安装的

进行源码安装,参考

https://blog.csdn.net/daoshengtianxia/article/details/115038674

在Downloads目录下克隆

git clone git://github.com/ntfreak/openocd

cd openocd/

安装依赖

然后执行

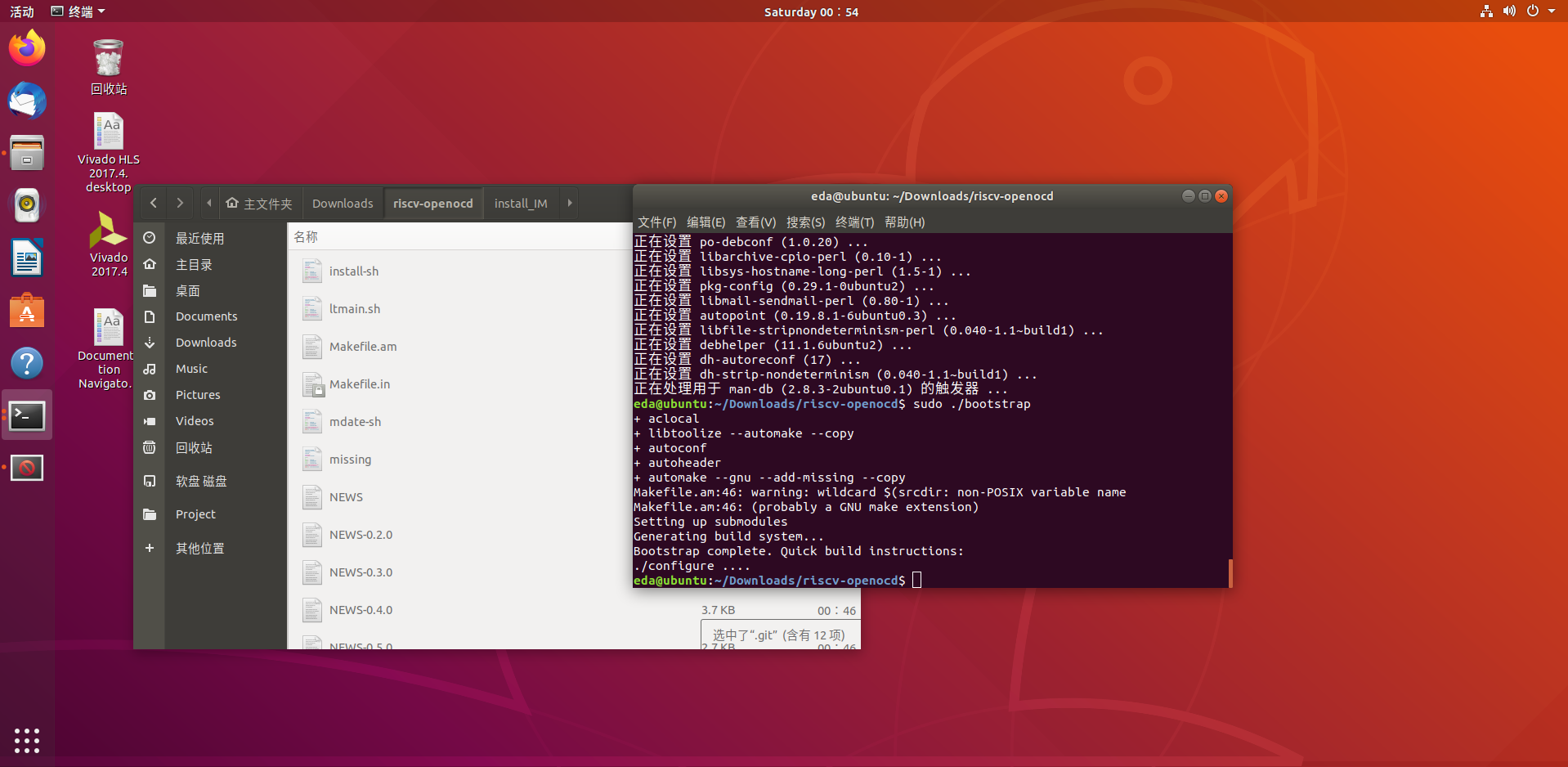

./bootstrap

缺少了什么但又不清楚,补充安装了一大堆东西。

sudo apt install debhelper findutils autotools-dev autoconf automake libtool pkg-config libltdl-dev

重新执行

./bootstrap

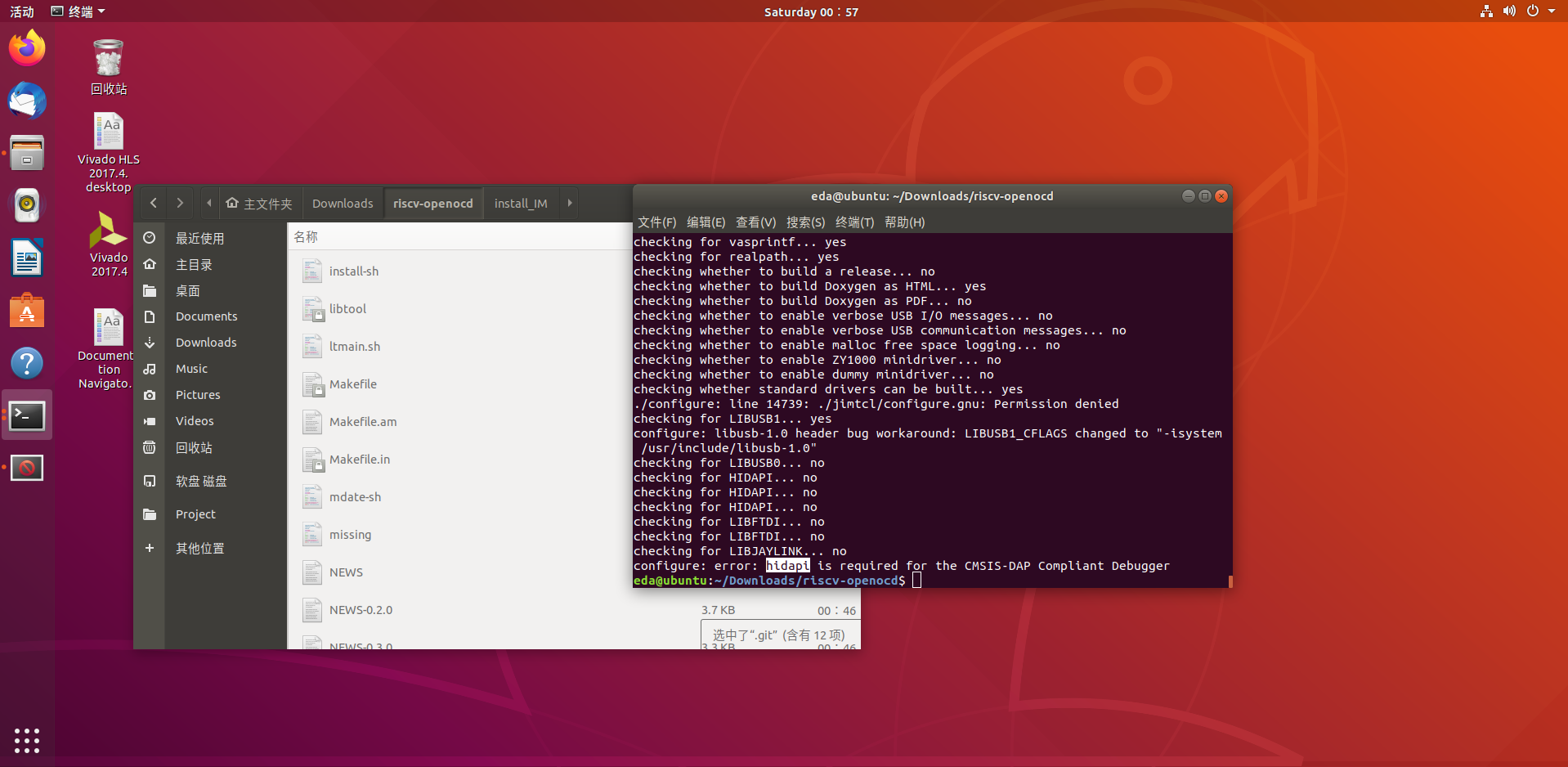

缺少libusb-1.x,补充安装

sudo apt install libusb-1.0

再次configure

这次应该是顺利配置了

再补充下面这个

./configure –enable-cmsis-dap –enable-jlink –enable-stlink –enable-ti-icdi

提示需要hidapi,

sudo apt-get install libhidapi-dev

其实是要补充安装这个libhidapi的库,然后再配置。注意一定要给权限。

sudo ./configure –enable-cmsis-dap

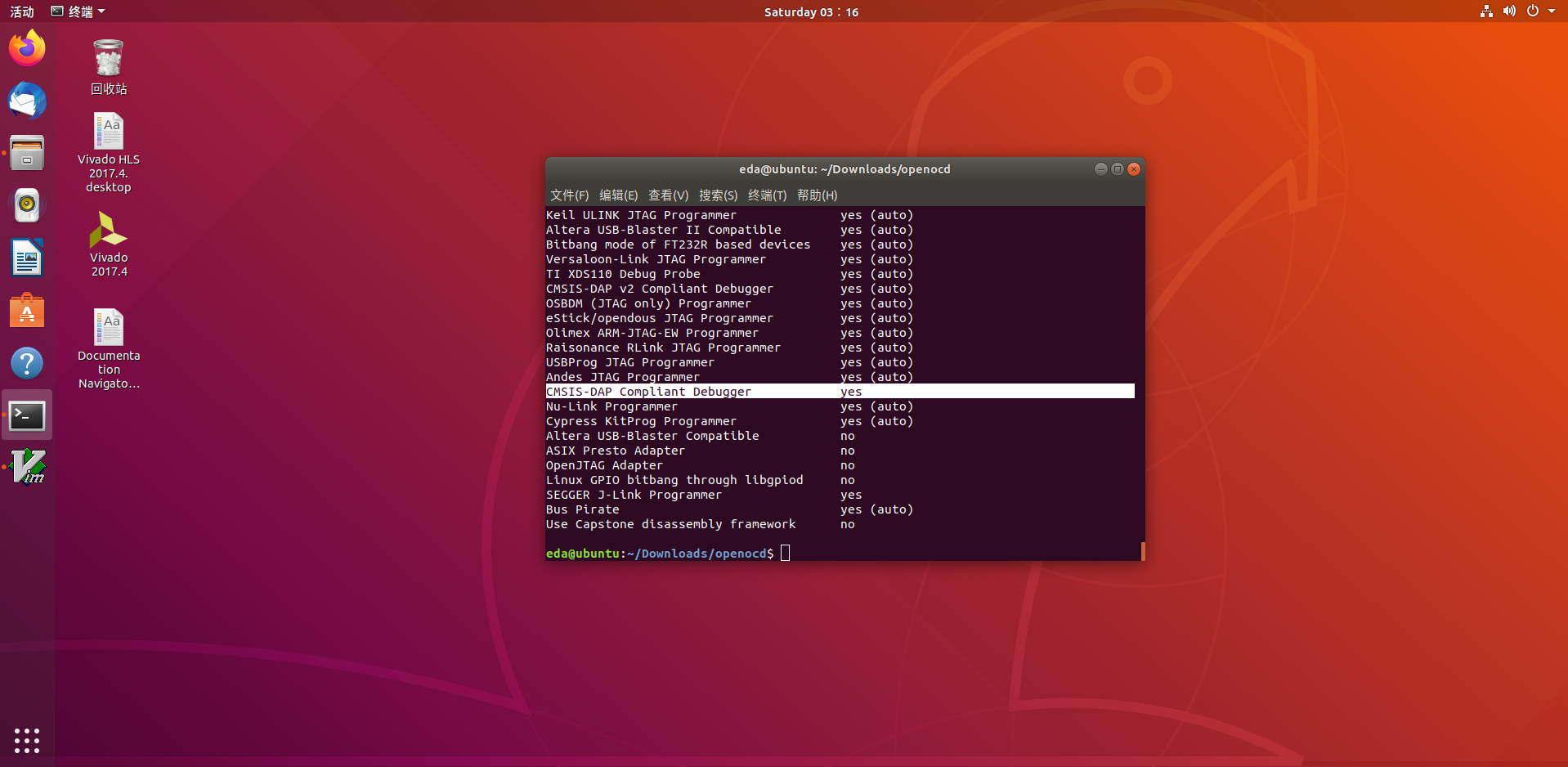

配置成功一定要看到这个地方是yes的

最后编译安装

sudo make&make install

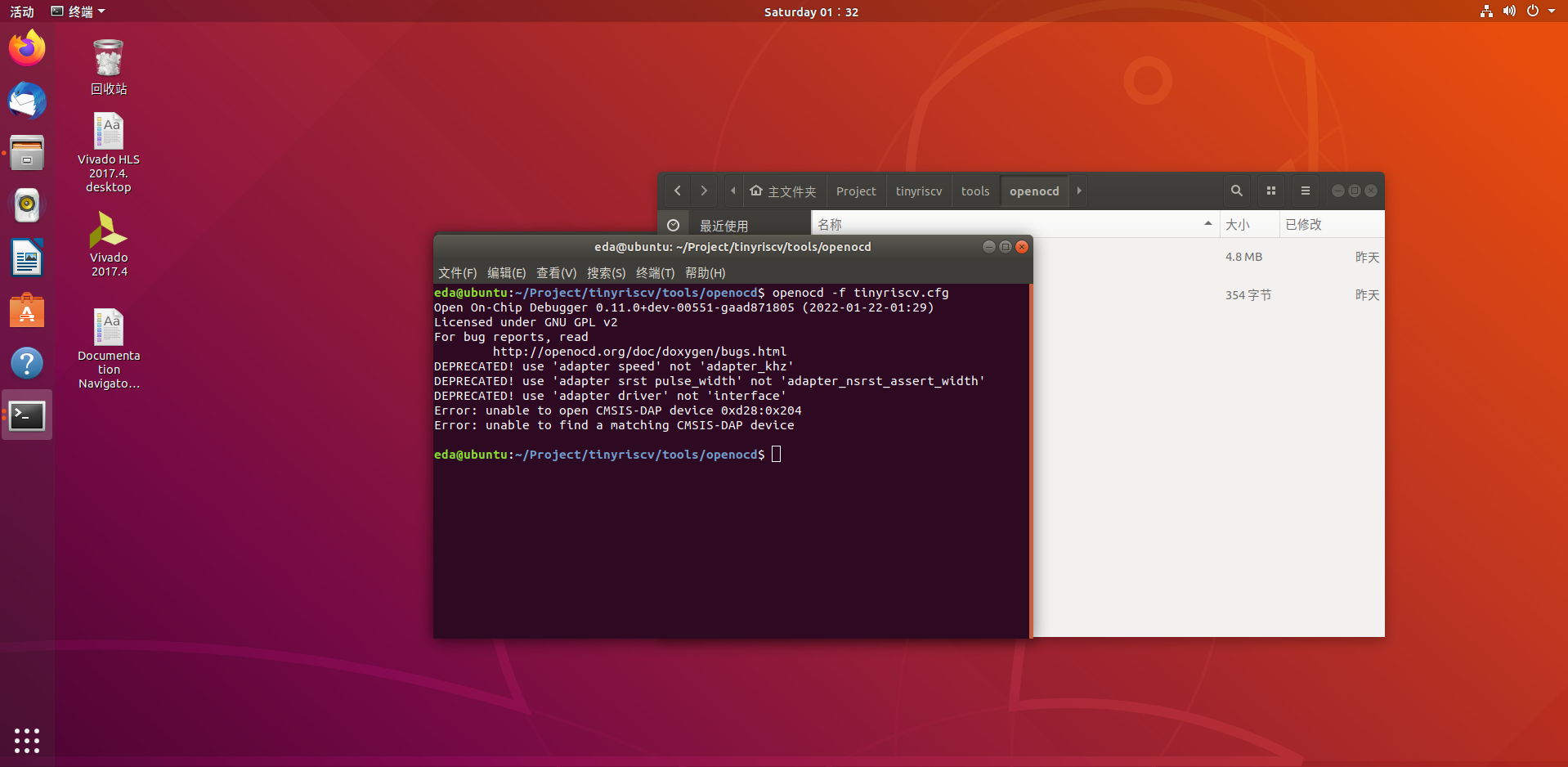

完成安装以后,回到tinyriscv/tools/openocd目录下

openocd -f tinyriscv.cfg

现在可以启用这个软件了,当然目前连接还是失败的,需要再做一些配置。

此外,首先需要对.cfg文件中的一些内容做修改。

根据上一张图,有提示说use”adapter speed”not’adapeter_khz’

意思就是用前面那个不要用后面那个表述,

打开.cfg就可以看到对应的内容了,改过来就行。

然后还需要准备权限,参考https://www.bbsmax.com/A/A2dm9B87de/

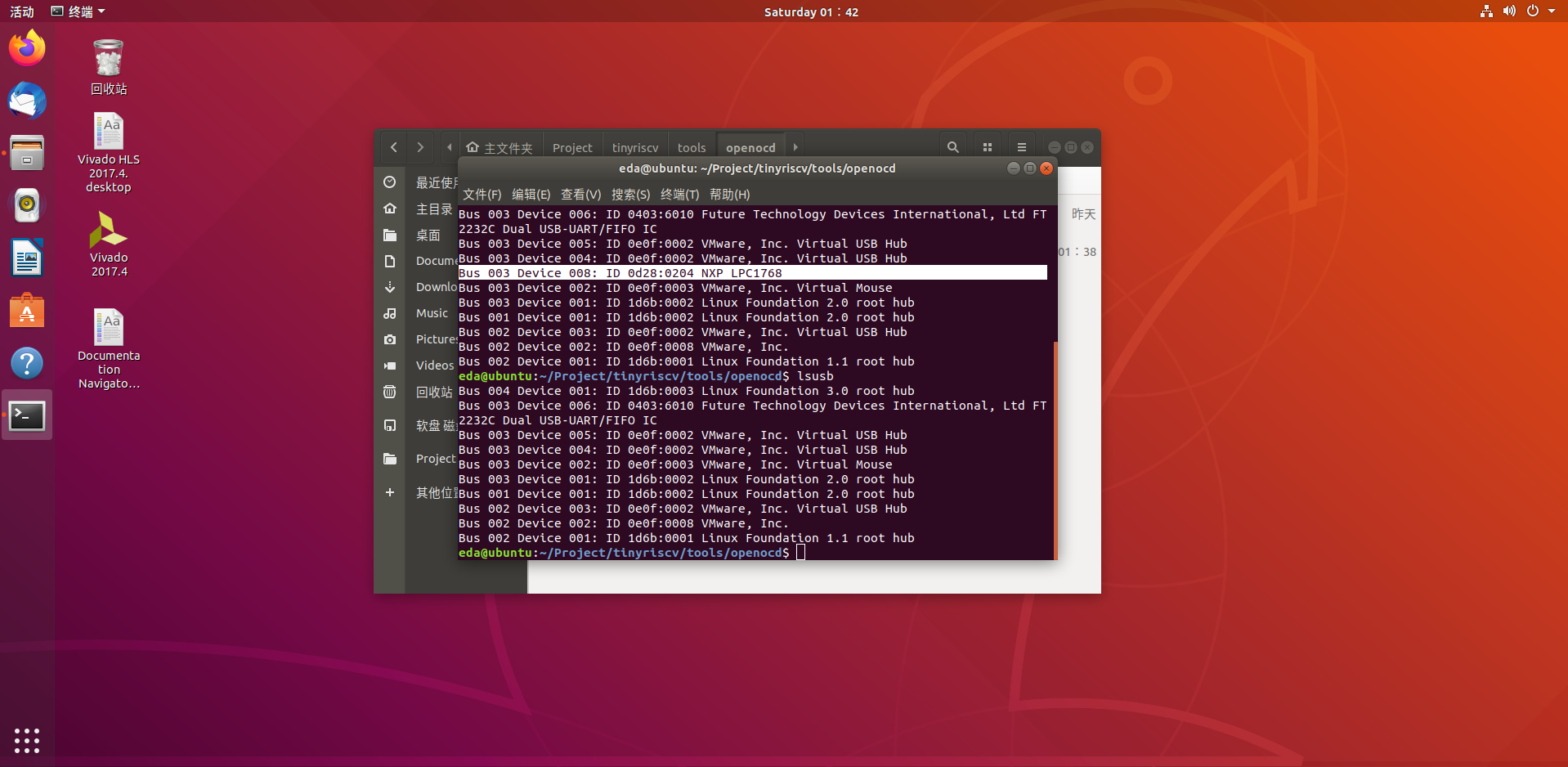

用lsusb

确认自己的调试器信息

Bus 003 Device 008: ID 0d28:0204 NXP LPC1768

需要增加一个rules文件,参考https://blog.csdn.net/zhengyangliu123/article/details/78232241

进入前面克隆的openocd/contrib 目录

使用指令将 60-openocd.rules 文件复制入 /etc/udev/rules.d/ 目录下

sudo cp 60-openocd.rules /etc/udev/rules.d/

然后,对文件做一些修改【此处存疑,可能不改也能用】

sudo gvim /etc/udev/rules.d/60-openocd.rules

最下面的地方,改成跟我下图一样的。

注意idVendor和idProduct要保持和上面看到的0d28:0204设备信息一致。

保存以后重启电脑

回到之前的tinyriscv中的openocd文件夹,使用终端执行

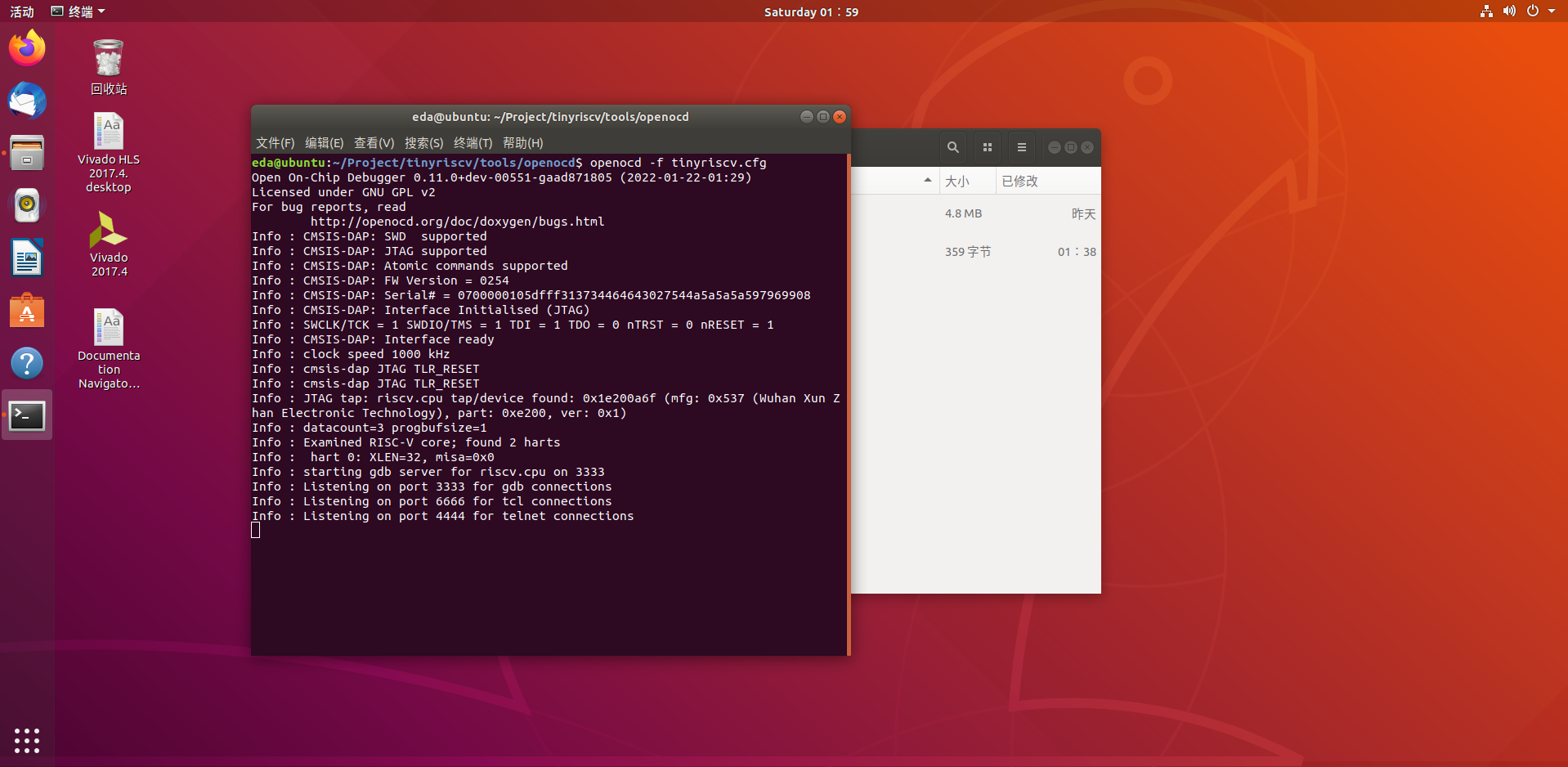

openocd -f tinyriscv.cfg

终于看到这个了,不容易啊

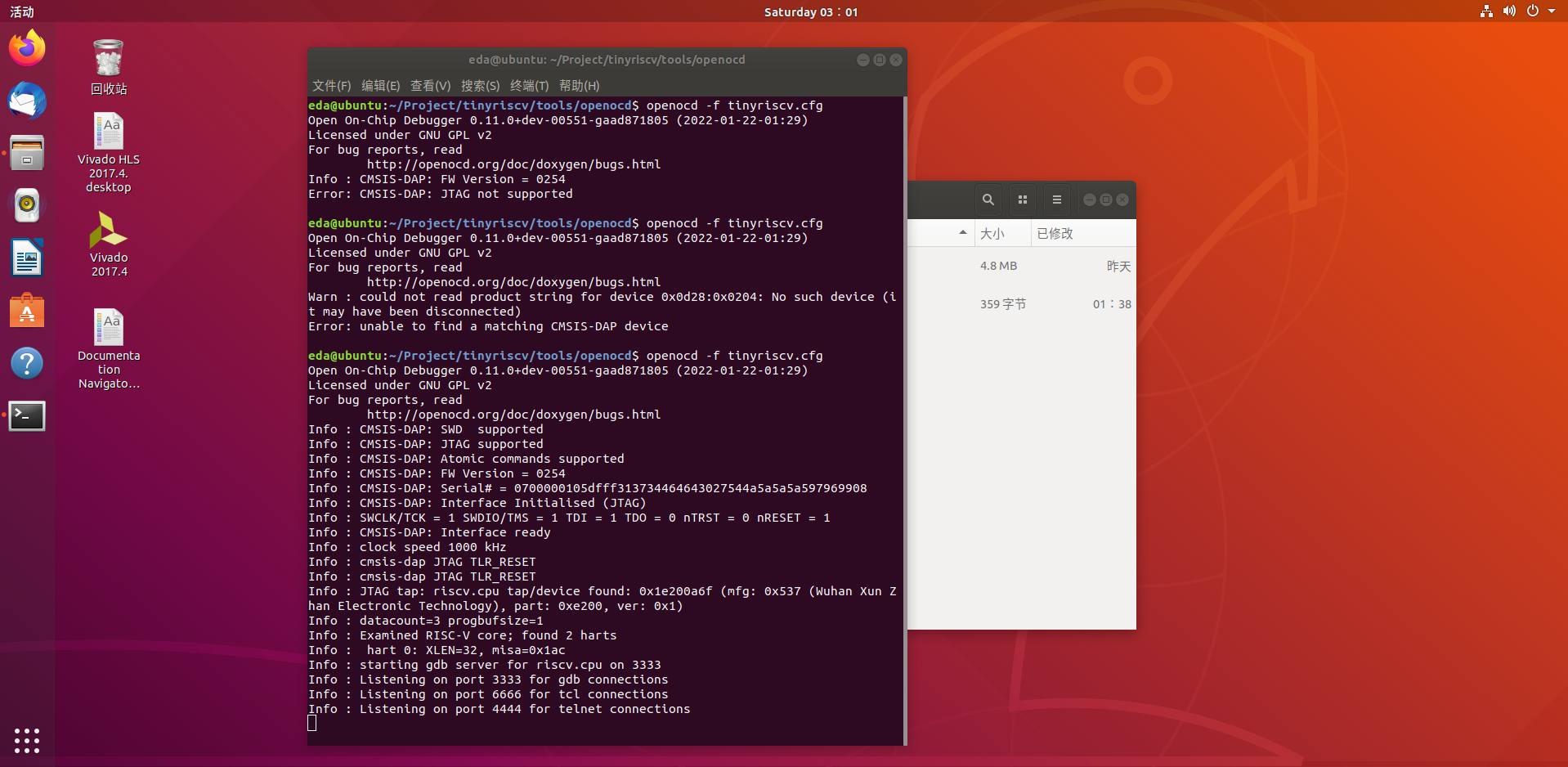

*注意,这里存在未知问题。每次重启系统以后,最开始使用openocd会报错。需执行3次,才会识别并启用……

原因不明,但每次都这样。只要启动成功,不关机就不会有这个问题。

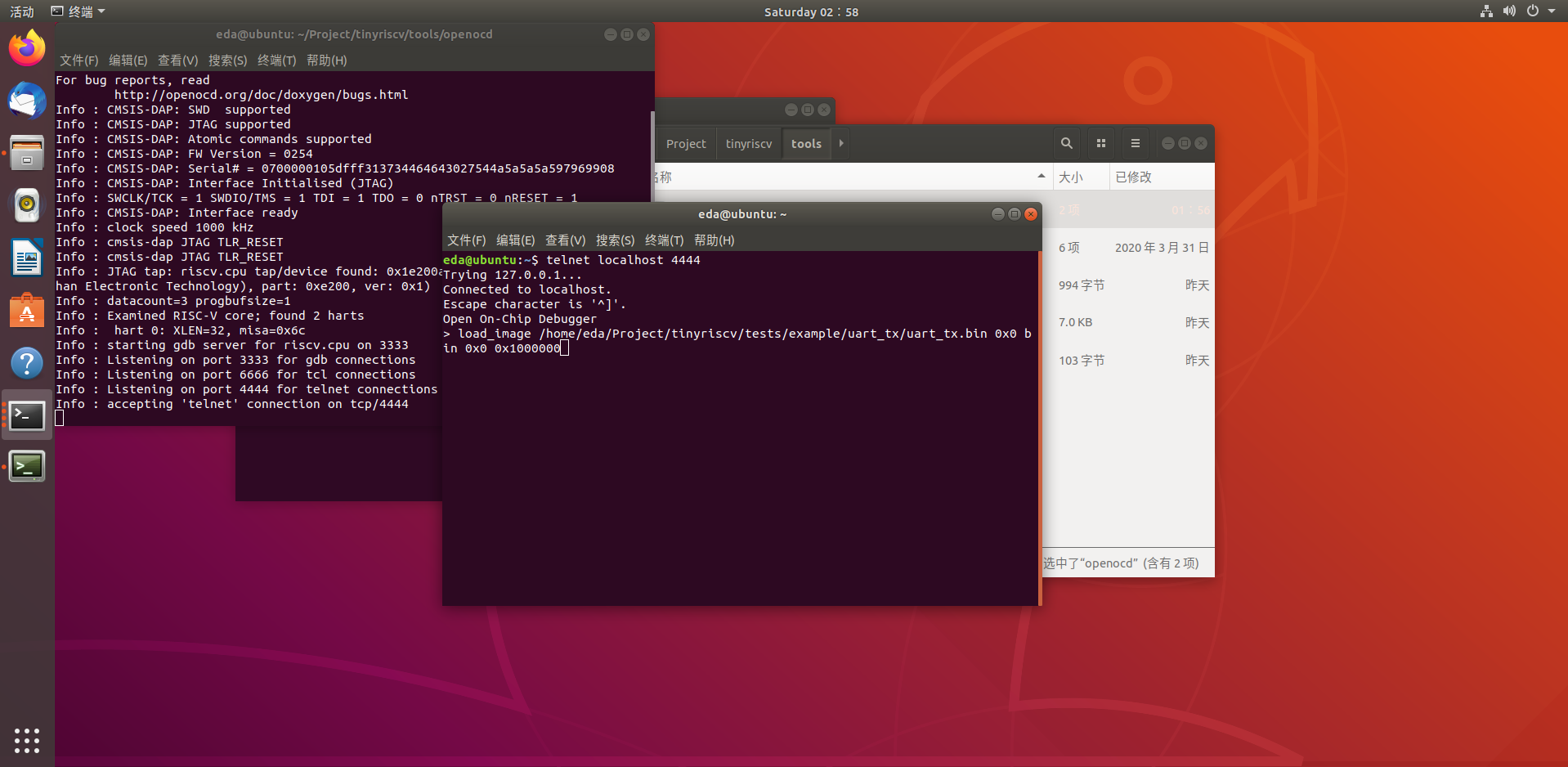

新开一个终端,看作者后续的操作。windows和linux在路径上有些不同

然后打开另一个CMD窗口,执行以下命令来连接openocd,注意电脑要启用telnet host服务。

telnet localhost 4444

然后在这个CMD窗口下使用load_image命令将固件下载到FPGA,这里以freertos.bin文件为例,如下所示:

load_image D:/gitee/open/tinyriscv/tests/example/FreeRTOS/Demo/tinyriscv_GCC/freertos.bin 0x0 bin 0x0 0x1000000

使用verify_image命令来校验是否下载成功,如下所示:

verify_image D:/gitee/open/tinyriscv/tests/example/FreeRTOS/Demo/tinyriscv_GCC/freertos.bin 0x0

如果下载出错的话会有提示的,没有提示则说明下载成功。

最后执行以下命令让程序跑起来:

resume 0

注意:每次下载程序前记得先执行halt命令停住CPU。;

这里使用gpio进行验证

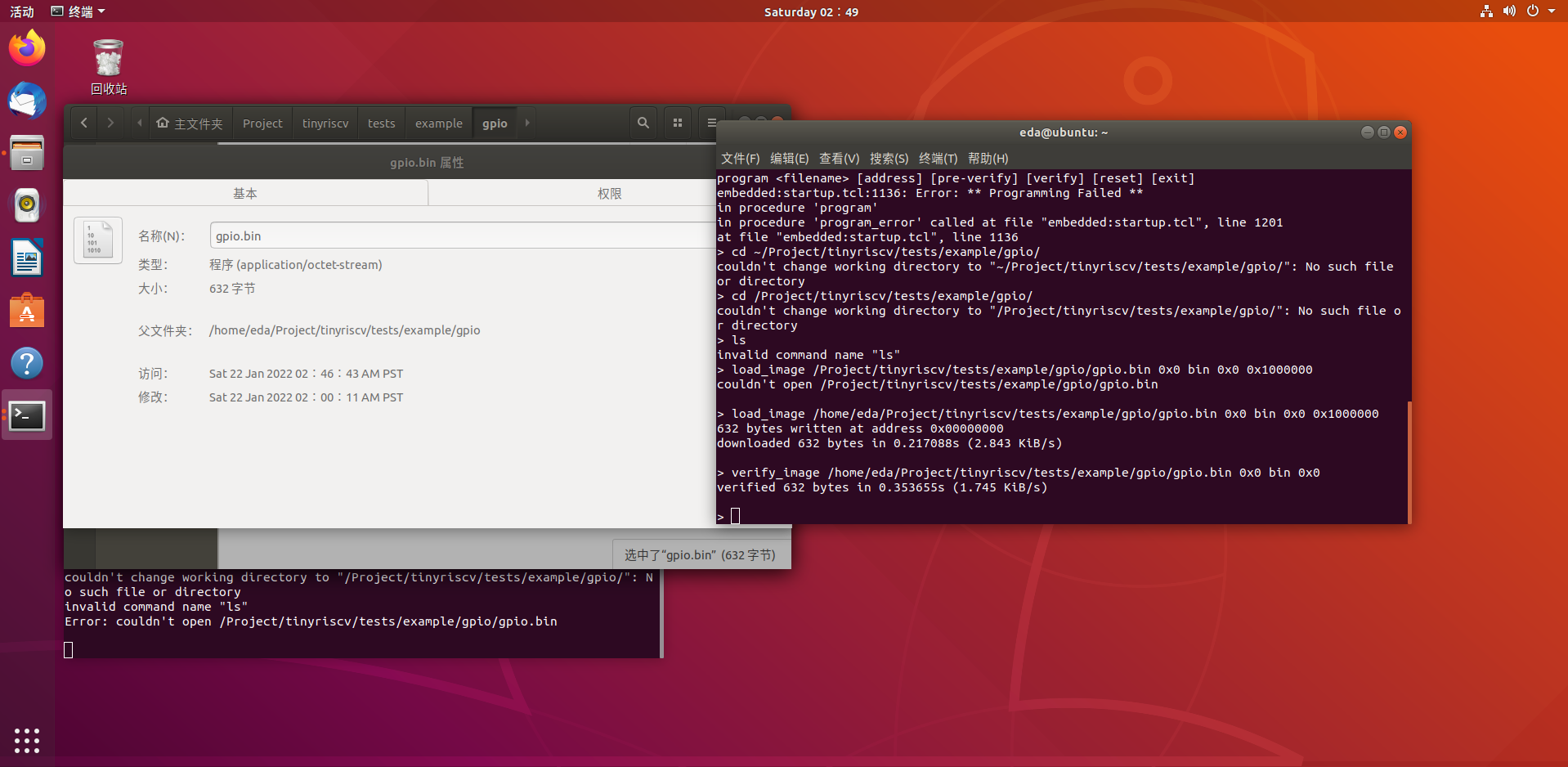

在/home/eda/Project/tinyriscv/tests/example/gpio路径下使用make编译生成bin文件

在telnet窗口下使用下面命令烧写程序

load_image /home/eda/Project/tinyriscv/tests/example/gpio/gpio.bin 0x0 bin 0x0 0x1000000

verify_image /home/eda/Project/tinyriscv/tests/example/gpio/gpio.bin 0x0 bin 0x0

如果看到这个,说明程序烧写成功了

resume 0

此时开发板已经可以正常使用,LED灯会随对应的那个开关亮灭。

下面测试一下串口,

先去把串口发送uart_tx的程序编译一下

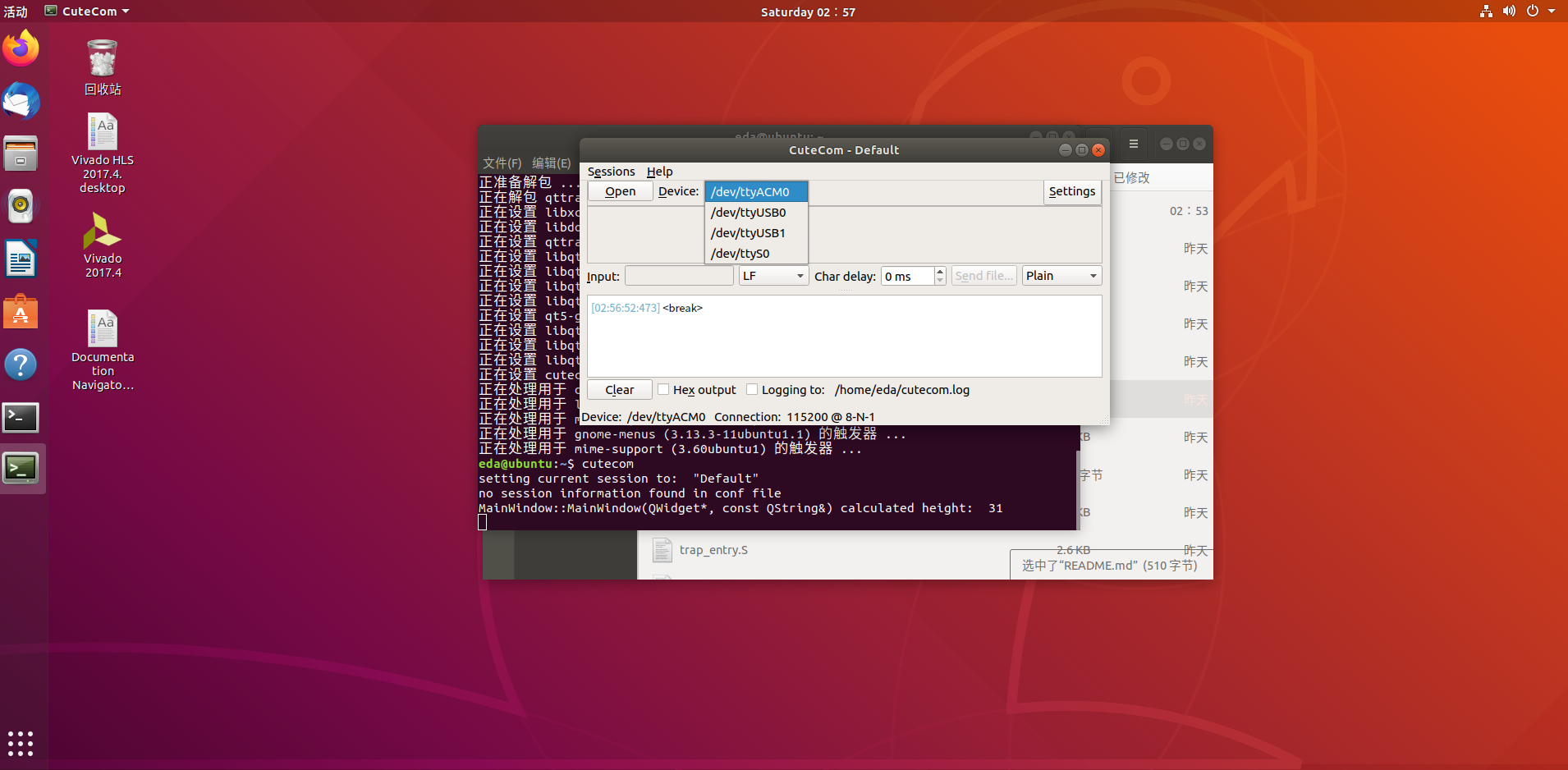

安装串口调试工具cutecom

sudo apt-get install cutecom

直接打开工具

选这个ACM

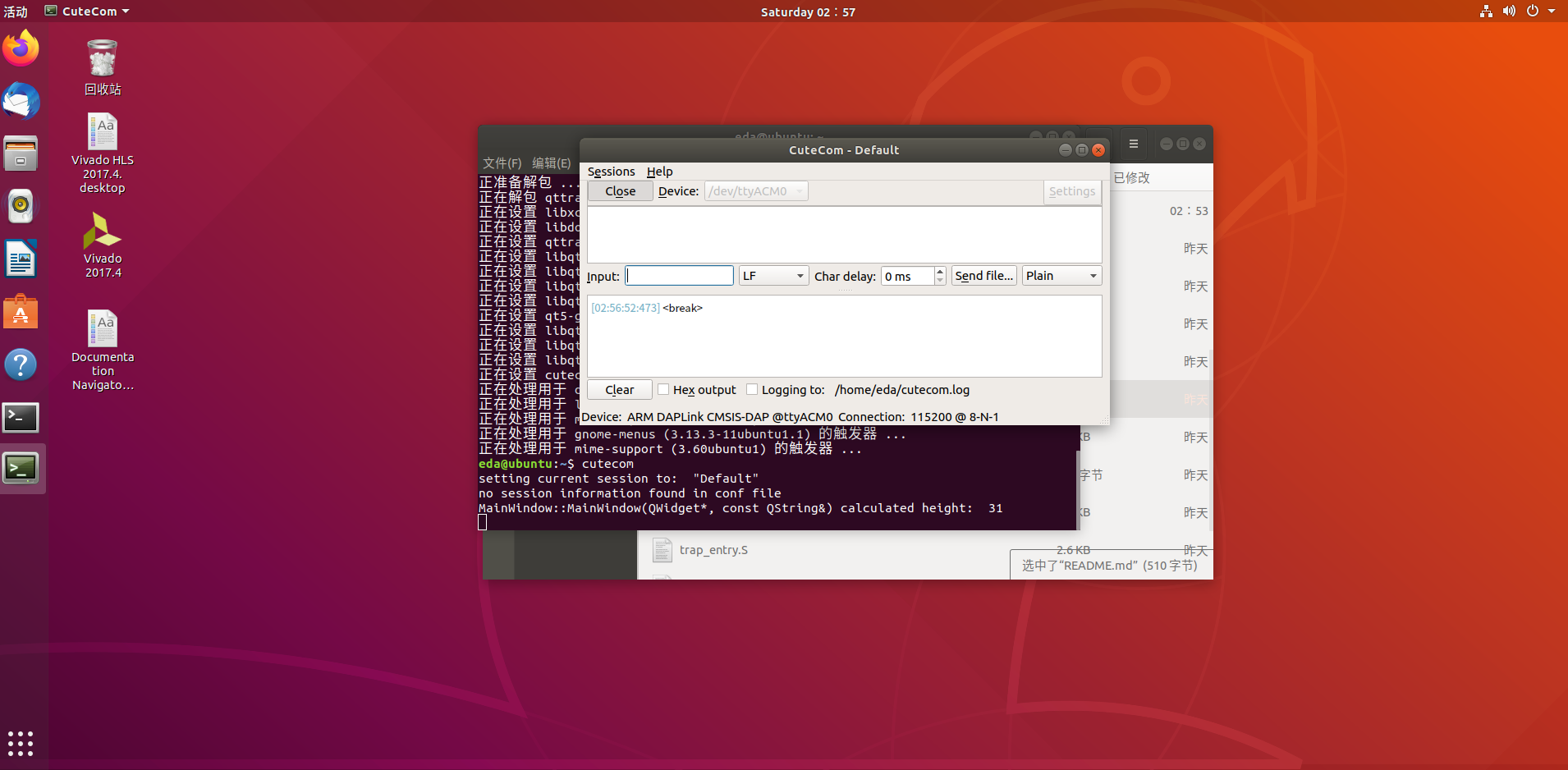

OPEN以后会看到,连接的就是这个CMSIS-DAP调试器

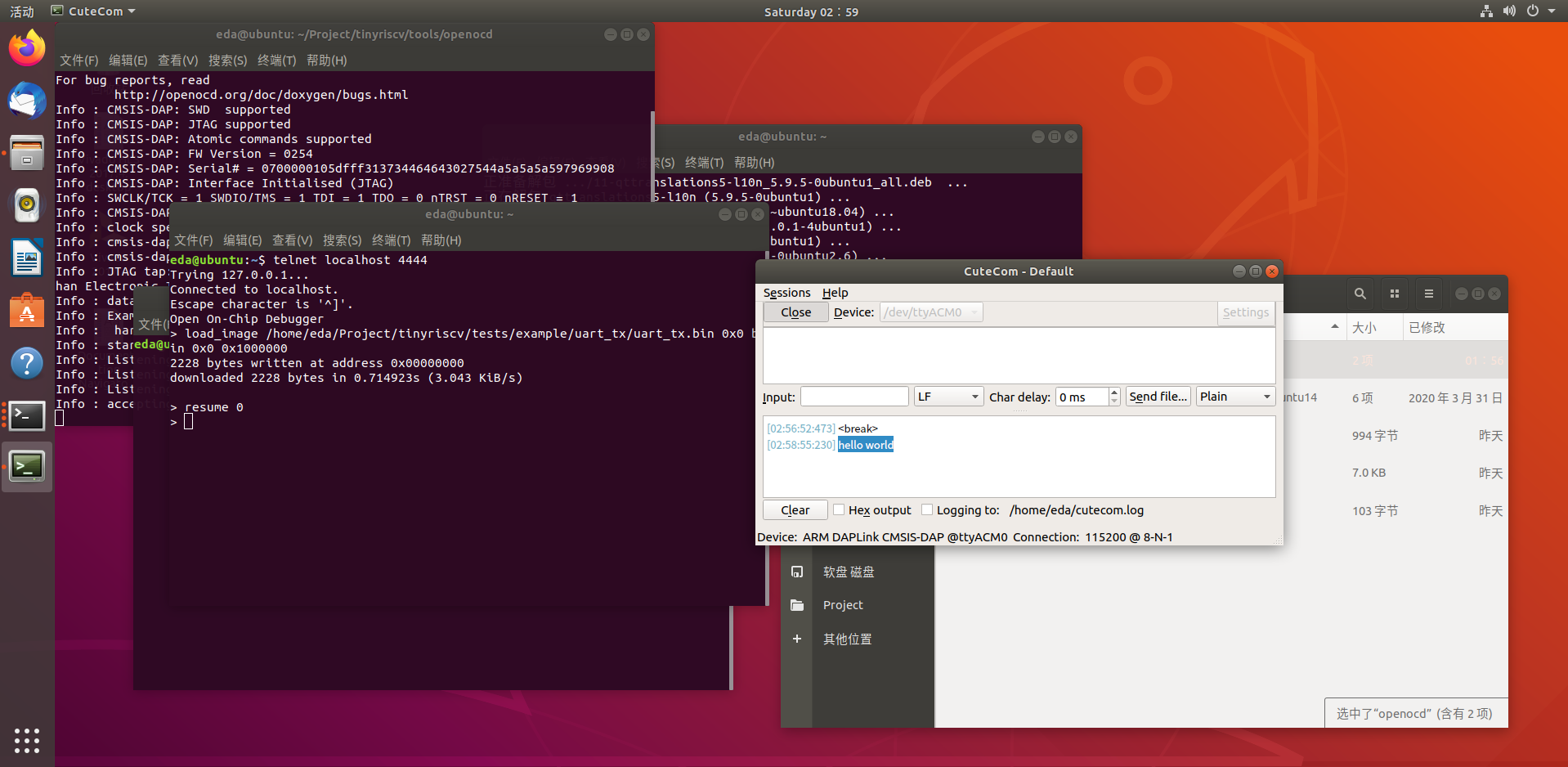

load_image /home/eda/Project/tinyriscv/tests/example/uart_tx/uart_tx.bin 0x0 bin 0x0 0x1000000

烧写进去并且resume以后,可以看到串口助手窗口打印了hello world。

至此,整个tinyriscv的linux开发环境搭建完成,可以运行整个项目的所有内容。

其他补充

输入su命令获取root权限时, 出现了

authentication failure 的问题,即身份验证失败。

需要进行下面操作:

$ sudo passwd root

Enter new UNIX password:

//此时输入你的密码

Retype new UNIX password:

//再次输入,相同密码。

passwd: password updated successfully

此时再用su命令,就可以获取到root权限了。