AXI协议学习笔记

ARM官方手册:AMBA AXI and ACE Protocol Specification

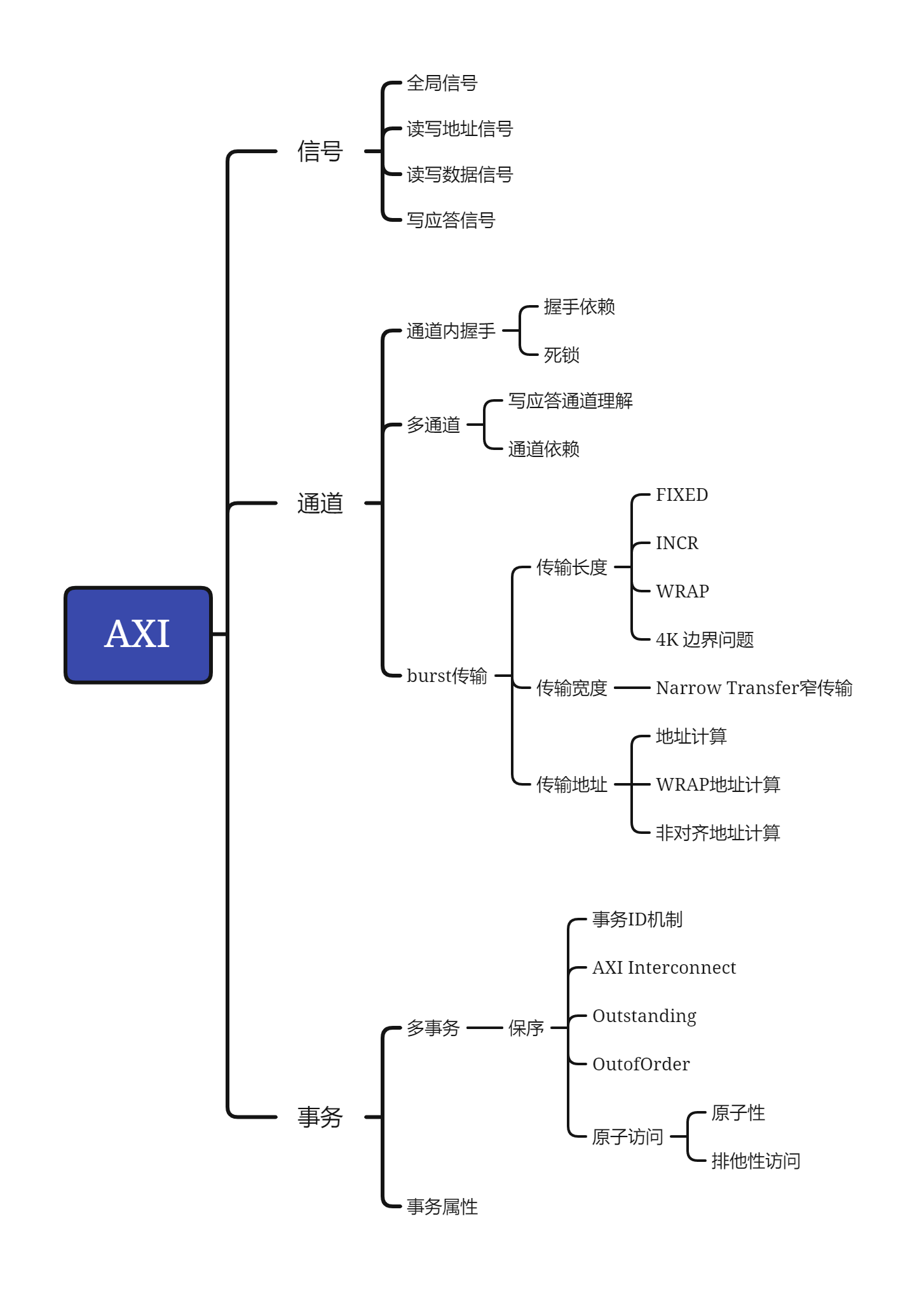

全景图

什么是AXI

AXI(Advance eXtensible interface)是一种总线协议,该协议是ARM公司提出的AMBA(Advanced Micocontroller Bus Architecture)协议中重要部分,是一种面向高性能、高带宽、低延迟的片内总线。

当前,SoC中绝大多数对性能有需求的模块都会使用到AXI。

为什么要选择AXI

AXI的性能只是一个方面的原因,另外一个重要因素其实是市场环境。

- 所拥有的IPs总线协议

- 所涉及的处理器总线协议。

- 总线的应用率,市场占有率。

- 总线的性能。

- 兼容性。

AXI总线协议是当前市场上能满足上述因素的一个强大协议,所以身为IC工程师,对AXI的掌握可以说是必须的。

AXI和AHB的区别

参考文献:AMBA AHB协议和AXI协议有什么区别? - 极术社区 - 连接开发者与智能计算生态

AXI的架构

传输通道

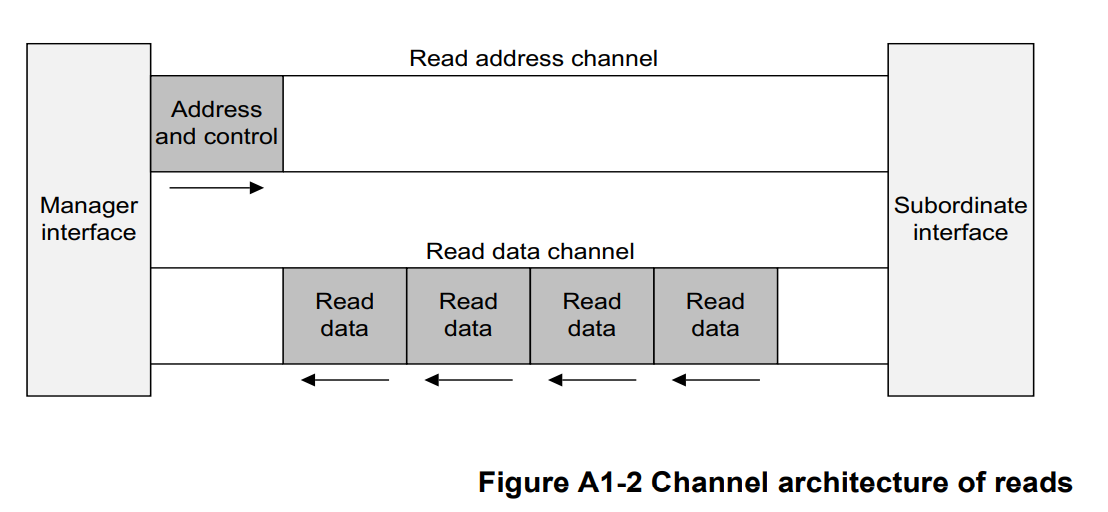

AXI具有五个数据通道,各通道之间是并行的,相当于独立的五条总线。

每条通道都具有固定的方向。

读操作包括AR读地址(命令)和R读数据通道,

写操作包括AW写地址(命令)、W写数据、B写响应通道。

AR/AW不仅仅包含地址信息,还包含控制,所以应该视为命令通道。

读数据通道传输数据和读应答,读应答指示每拍数据的状况。

写数据通道和写应答通道分离,写应答指示每burst数据的状况。

由于AXI各通道都是单向传输的,且各通道之间相位分离,没有复杂的时序握手关系。这种特性使得各通道可以随意插入任意级数寄存器(stage),即打拍,来保证时序收敛。

写响应通道独立的原因

核心原因:写响应数据流向和写数据数据流向是相反的。

互联结构

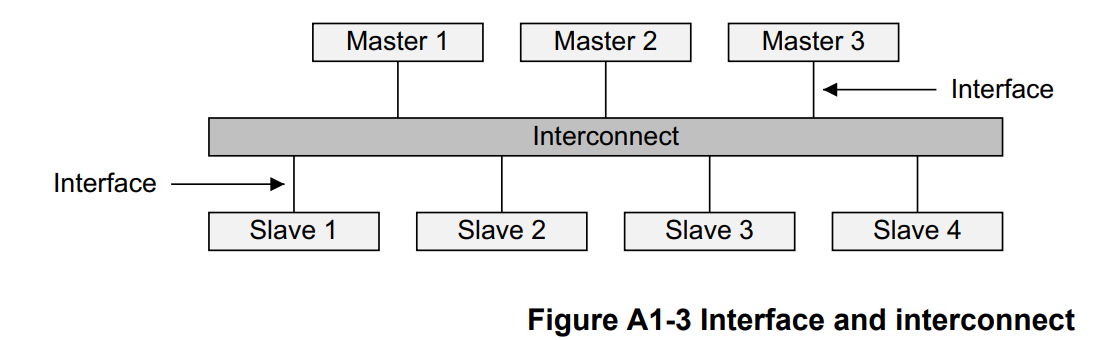

AXI协议严格来讲是一个点对点的主从接口协议,当多个外设需要互联时,需要加入一个AXI Interconnect模块,也就是AXI互联矩阵,作用是提供一个或多个AXI主设备连接到一个或多个AXI从设备时得一种交换机制。

AXI端口信息

GLOBE全局信号

| Signal | Source | Description |

|---|---|---|

| ACLK | 系统时钟 | 系统时钟信号,上升沿触发 |

| ARESETn | 系统复位 | 系统复位信号,低有效 |

AXI写/读地址通道(命令通道)

| Signal | Source | Description |

|---|---|---|

| AxID | Master | 传输地址ID,用于标识;相同ID需进行保序 |

| AxADDR | Master | 传输地址,该地址给出了突发事务中第一次传输的地址 |

| AxLEN | Master | 突发传输长度;实际长度=AxLEN+1 |

| AxSIZE | Master | 传输数据的size,单位为byte。 0->1bytes; 1->2byte; 2->4bytes; 3->8bytes; 4->16bytes; 5->32bytes;6->64bytes;7->128bytes |

| AxBURST | Master | Burst传输的模式: FIXED固定模式(00);INCR增量模式(01);WRAP卷绕模式(10) |

| AxLOCK | Master | AXI4不支持锁定传输,支持Exclusive独占传输 |

| AxPROT | Master | 保护类型,指示传输事务为PROT[0]: 1特权,0 非特权 |

AXI写/读数据通道

AXI写响应通道

AXI低功耗信号

略

基本读写事务

握手机制

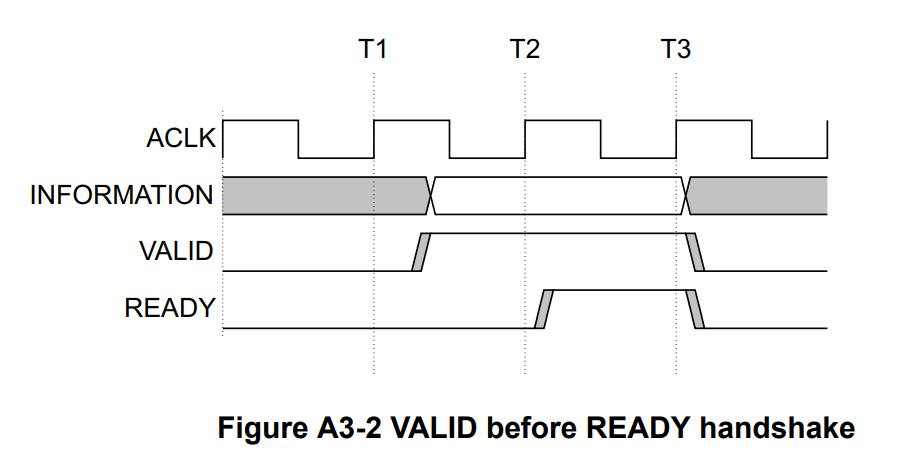

在握手机制中,通信双份分别扮演发送方和接收方,两者的操作并不相同。

通常会设计AXI Master 和 SLV两种端口。

发送方置高VALID信号表示发送方已经将数据、地址或控制信息就绪,并保持于信息总线上。接收方置高READY信号表示接收方已经做好接收的准备。

READY可以早于或晚于VALID,也可以依赖VALID;

VALID可以早于或晚于READY,但不可以依赖READY,防止死锁。

所谓双向流控机制,指的时发送方通过置起VALID信号控制发送的时机与速度,接收方也可以通过READY信号的置起与否控制接收的速度。发送方拥有传输的主动权,但接收方在不具备接收能力时,也能够置低信号停止传输,反压发送方。

协议规定,在这种情况下,VALID信号一旦置起就不能置低,直到完成握手,至少传输一周期数据。

置起VALID信号必须是完全主动与独立的过程,否则就可能出现死锁。

死锁

待更新

规避死锁的方式

待更新

事务握手间的依赖关系

待更新

事务的结构

AXI是基于Burst传输的协议,传输的属性及首地址都通过地址通道发送。

Burst传输长度

FIXED

WRAP

INCR

Burst传输大小

待更新

Burst地址计算

待更新

Burst不能跨4K边界

待更新

AXI不支持提前终止Burst

待更新

写有效机制

待更新

窄带传输

待更新

字节不变性

待更新

地址非对齐

待更新

读写应答机制

待更新

保序机制

Outstanding超前传输

超前传输(Outstanding transaction)特性是AXI总线能够实现高性能传输的原因之一。

AxID保序

待更新

Interconnect ID扩展

待更新

AXI4保序模型

待更新

事务属性

属性域段

AxCACHE

不可修改事务

待更新

Read/Write allocated

待更新

memory类型

待更新

访问权限

待更新

Atomic Accesses 原子访问

原子性

待更新

Exclusive access排他性访问

待更新

为什么AXI4取消了Lock

待更新

AXI4新增信号

QoS

待更新

Multiple region interface

待更新

User-defined

待更新